将AXI流连接到StreamFifo

将AXI流连接到StreamFifo

提问于 2022-07-08 07:44:33

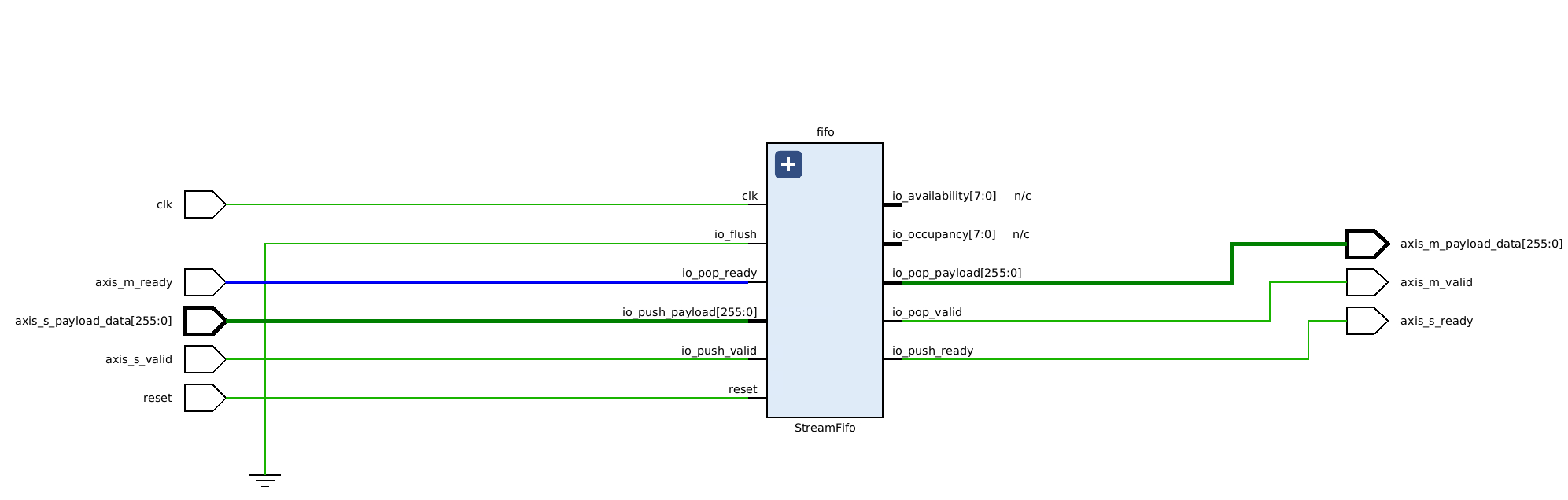

我想连接AXI流母版到流Fifo。我只需要有效载荷,有效的和现成的信号。其思想是用数据加载FIFO,并通过AXI流将其推送到逻辑的其他部分。

简单的例子:

case class AxiWithFifo() extends Component {

val io = new Bundle {

val axis_s = slave(

Axi4Stream(Axi4StreamConfig(dataWidth = 32))

)

val axis_m = master(

Axi4Stream(Axi4StreamConfig(dataWidth = 32))

)

}

val fifo = StreamFifo(dataType = Bits(256 bits), depth = 128)

fifo.io.push << io.axis_s.toBitStream()

io.axis_m.toBitStream() << fifo.io.pop

}令人遗憾的是,有人抱怨等级制度的违反:

[#25] HIERARCHY VIOLATION : (toplevel/io_axis_m_ready : in Bool) is driven by (toplevel/??? : Bool), but isn't accessible in the toplevel component.

[#25] spinal.lib.Stream.arbitrationFrom(Stream.scala:304)

[#25] spinal.lib.bus.amba4.axis.Axi4Stream$Axi4StreamRich.toBitStream(Axi4Stream.scala:131)

[#25] spinalhdlexample.AxiWithFifo.<init>(AxiWithFifo.scala:40)

[#25] spinalhdlexample.AxiWithFifo$.$anonfun$main$1(AxiWithFifo.scala:47)

[#25] spinal.sim.JvmThread.run(SimManager.scala:51)有什么办法解决吗?

回答 1

Stack Overflow用户

发布于 2022-07-08 10:07:29

因此,部分解决方案是从流中产生流,并手动连接流信号。

case class AxiWithFifo() extends Component {

val io = new Bundle {

val axis_s = slave(

Axi4Stream(Axi4StreamConfig(dataWidth = 32))

)

val axis_m = master(

Axi4Stream(Axi4StreamConfig(dataWidth = 32))

)

}

noIoPrefix()

val fifo =

StreamFifo(

dataType = Bits(256 bits),

depth = 128

)

fifo.io.push << io.axis_s.toBitStream()

val fifoFlow = fifo.io.pop.toFlow

when(fifo.io.pop.valid) {

io.axis_m.valid := True

}.otherwise {

io.axis_m.valid := False

fifoFlow.setIdle()

}

when(io.axis_m.ready) {

fifo.io.pop.ready := True

}.otherwise {

fifo.io.pop.ready := False

}

io.axis_m.payload.data <> fifoFlow.payload

}

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/72908239

复制相关文章

相似问题