任务不传递输出权限。

任务不传递输出权限。

提问于 2022-06-15 18:14:08

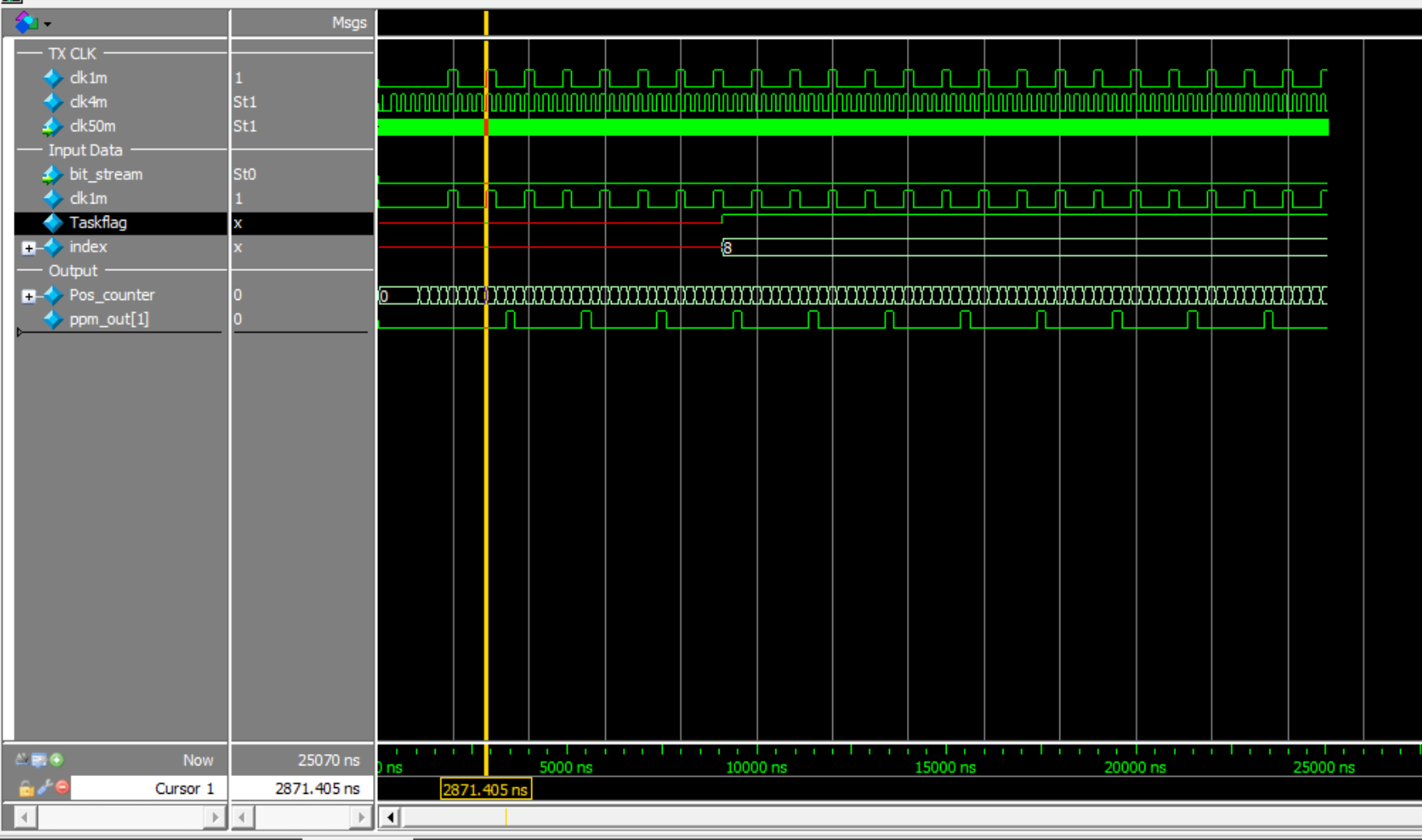

我一直在尝试为我的测试台设计一个任务,以使我的生活更轻松。当我使用$display检查内部信号时,任务似乎做得很好。但是,当我将任务挂在initial块中时,显示在波形上的仿真输出与显示结果不一样。提前谢谢你

===========Code===========

`timescale 1ns/1ps

/*----------Macros----------*/

`define FullCycle 20

`define HalfCycle 10

`define CLK_Cycle(CycleNum) (`FullCycle*CycleNum)

module syncronization_tb();

/*----------DUT I/O----------*/

logic reset_n, clk4m, ppm_data, output_valid_flag;

logic [7: 0] data_out_DUT;

logic flag;

/*----------TX I/O----------*/

logic bit_stream, clk50m;

logic [1: 0] ppm_out;

/*----------RX I/O----------*/

logic clk50mREC;

logic data_out;

assign ppm_data = data_out;

Syncronization DUT

(

reset_n,

clk4m_out,

ppm_data,

data_out_DUT,

output_valid_flag

);

PPM_top TX

(

reset_n,

clk50m,

bit_stream,

ppm_out

);

CLK_Recovery RX

(

clk50mREC,

reset_n,

ppm_out[1],

data_out,

clk4m_out

);

logic [7:0] data;

logic Taskflag;

integer index;

initial forever #`HalfCycle clk50m = ~ clk50m;

initial #17 forever #`HalfCycle clk50mREC = ~clk50mREC;

initial begin

{reset_n, clk50m, bit_stream, clk50mREC} = 0;

#`CLK_Cycle(5);

{reset_n} = 1;

data = 8'haa;

generateBITstream(.data(data), .bit_stream_out(bit_stream),.index(index));

// data = 8'he3;

// generateBITstream(data, bit_stream);

//data = 8'h5b;

//generateBITstream(data, bit_stream);

#`CLK_Cycle(800);

$stop;

end

task automatic generateBITstream;

parameter integer width = 8;

input [width - 1: 0] data;

output logic bit_stream_out;

output integer index;

begin

for(index = 0; index < width; index = index + 1 ) begin

@(posedge TX.clk1m) bit_stream_out = data[index];

$display("%d and time is %t with %b",index, $time, bit_stream_out);

#`CLK_Cycle(10);

end

end

endtask

endmodule===========Console显示正确的Result===========

run -all

# 0 and time is 1870000ps with 0

# 1 and time is 2870000ps with 1

# 2 and time is 3870000ps with 0

# 3 and time is 4870000ps with 1

# 4 and time is 5870000ps with 0

# 5 and time is 6870000ps with 1

# 6 and time is 7870000ps with 0

# 7 and time is 8870000ps with 1

# Break in Module syncronization_tb at G:/Work/PPM/src/Syncronization RTL Simulation/src/syncronization_tb.sv line 74===========Waveform错误Result===========

[

]

===========A最小可重复性example===========

`timescale 1ns/1ps

/*----------Macros----------*/

`define FullCycle 20

`define HalfCycle 10

`define CLK_Cycle(CycleNum) (`FullCycle*CycleNum)

module syncronization_tb();

logic [7:0] data;

logic bit_stream, clk50m;

integer index;

initial forever #`HalfCycle clk50m =~ clk50m;

initial begin

clk50m = 0; #`CLK_Cycle(10);

data = 8'haa;

generateBITstream(.data(data), .bit_stream_out(bit_stream),.index(index));

#`CLK_Cycle(800);

$stop;

end

task automatic generateBITstream;

parameter integer width = 8;

input [width - 1: 0] data;

output logic bit_stream_out;

output integer index;

begin

for(index = 0; index < width; index = index + 1 ) begin

@(posedge clk50m) bit_stream_out = data[index];

$display("%d and time is %t with %b",index, $time, bit_stream_out);

#`CLK_Cycle(10);

end

end

endtask

endmodule===========Console显示正确的Result===========

# 0 and time is 210000 with 0

# 1 and time is 410000 with 1

# 2 and time is 610000 with 0

# 3 and time is 810000 with 1

# 4 and time is 1010000 with 0

# 5 and time is 1210000 with 1

# 6 and time is 1410000 with 0

# 7 and time is 1610000 with 1

# Break in Module syncronization_tb at G:/Work/PPM/src/Syncronization RTL Simulation/src/syncronization_tb.sv line 22回答 1

Stack Overflow用户

回答已采纳

发布于 2022-06-15 18:40:00

问题是,连接到任务输出端口(bit_stream)的信号只有在任务完成后(在for循环之后)才会在testbench中得到更新。它并不是每次在$display循环中调用for时都会更新。

解决这一问题的一种方法是摆脱任务输出端口,直接更新任务内部的bit_stream信号:

task automatic generateBITstream;

parameter integer width = 8;

input [width - 1: 0] data;

output integer index;

begin

for(index = 0; index < width; index = index + 1 ) begin

@(posedge TX.clk1m) bit_stream = data[index];

$display("%d and time is %t with %b",index, $time, bit_stream);

#`CLK_Cycle(10);

end

end

endtask 然后将任务调用为:

generateBITstream(.data(data), .index(index));页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/72636058

复制相关文章

相似问题