高位表小信号档位的信号链设计札记

我昨天写了一篇:

其实这个问题蛮有趣,还可以往下引申更多讨论,接下来就深化一点;这次不再假设前端截止频率 10 Hz,而是直接按 DVM1107 的 PLC 来看。

已知:DVM1107 读数速度为 1–100 PLC,对应 0.5–40 sps;噪声表是按 10 PLC 给出的;100 mV 档在 10 PLC 条件下,标准方差为 0.6 ppm,峰值噪声 0.7 μV p-p。

所以,最应该分析的就是 10 PLC。

先把 10 PLC 变成等效带宽

按前面的近似:

50 Hz 下,10 PLC = 0.2 s

60 Hz 下,10 PLC = 0.1667 s

所以,50 Hz 下:

60 Hz 下:

也就是说,DVM1107 在 10 PLC 的真实工作点上,前端看到的有效测量带宽更像:

这比前面假设的 10 Hz 窄得多,所以前端白噪声预算其实会更宽松一些。

重新建立 100 mV 档噪声

还是用前面的输入等效模型:

其中白噪声部分现在按 2.5 Hz 或 3 Hz 带宽算,而不是 10 Hz。

先看 DVM1107 自己的本底对应什么水平;100 mV 档、10 PLC 下的标准方差是 0.6 ppm,换算成电压:

所以整机自身本底大约是:

这就是前端预算的参照物,如果希望前端“不明显影响”,仍然建议让前端噪声控制在:

这样总噪声只会轻微增加。

用更贴近实际的 10 PLC 带宽重算实例,继续用前面那组前端参数:

运放白噪声密度:

电流噪声密度:

串联保护/滤波电阻:

分别算三种源阻抗:10 Ω,100 Ω,1 kΩ

以 50 Hz 电网、10 PLC、 为例

运放白噪声

100 Ω 串联电阻热噪声,用近似公式:

所以:

情况 A:

源阻抗热噪声

电流噪声项

白噪声合成

如果再加上比较现实的慢扰动预算:热电势波动6 nV rms+工频/EMI残余4 nV rms

则:

这非常好。

情况 B:

源阻抗热噪声

电流噪声项

白噪声合成

再加同样的慢扰动:

也非常好。

情况 C:

源阻抗热噪声

电流噪声项

白噪声合成

再加上热电势与外界耦合:

这个也仍然低于 15–20 nV 目标,把 10 PLC 下结果整理成表

50 Hz 下,10 PLC,

项目 | 10 Ω源 | 100 Ω源 | 1 kΩ源 |

|---|---|---|---|

源阻抗热噪声 | 0.64 nV | 2.02 nV | 6.40 nV |

100 Ω串联电阻热噪声 | 2.02 nV | 2.02 nV | 2.02 nV |

运放白噪声 | 1.58 nV | 1.58 nV | 1.58 nV |

电流噪声项 | 0.087 nV | 0.158 nV | 0.87 nV |

白噪声合成 | 2.64 nV | 3.27 nV | 6.95 nV |

加热电势6 nV + EMI 4 nV 后 | 7.7 nV | 7.9 nV | 10.0 nV |

前面我们按 10 Hz 带宽算时,1 kΩ 源阻抗已经比较紧张;但现在按 DVM1107 真正的 10 PLC 工作点去看,由于带宽只有 2.5–3 Hz,白噪声整体下降了很多。

这说明:

如果用 DVM1107 做慢速高精度 DC 采集,前端白噪声压力其实没有之前按 10 Hz 假设时那么大。

真正更难压住的,反而变成:热电势波动,低频 1/f 噪声这些,也就是:10 PLC 模式下,白噪声往往已经不是第一大敌人,慢漂才是。

再看一个“普通一点”的前端,会怎样?

现在把前端运放换成不那么极限的参数: ; 其他不变。

运放白噪声

重新算白噪声合成

10 Ω源

100 Ω源

1 kΩ源

即便这样,在 10 PLC 下也还不算差,这再次说明:窄带测量真的很占便宜;但要注意,这里还没把 0.1–10 Hz 噪声、chopper spur、热电势慢漂大幅加进去,所以并不意味着“普通运放就一定够”。

如果直接按 DVM1107 的 10 PLC 实际工作方式来定前端,可以把目标写成这样:

白噪声目标,让前端白噪声控制在:

这已经很好了。

总噪声目标,连同慢漂一起,最好控制在:

这时和 DVM1107 自己的 60 nV rms 本底相比,前端基本不会构成明显拖累;把 DVM1107 的 10 PLC 带宽因素加进去以后,可以得到一个比前面更真实的结论:对 100 mV 档如果是慢速精密测量,前端并不需要夸张到“白噪声 1 nV 以内、所有电阻都极低”那种程度。

代入 DVM1107 的实际 10 PLC 测量带宽后,100 mV 档前端更合理的目标不是原来宽带假设下的 20 nV 白噪声,而是:

这样前端基本不会明显影响 DVM1107 在 100 mV 档的采集效果。

一个新的点

今天讨论的和昨天讨论的,都是很硬性的指标,就是在极小的 100mV 进行高分辨率的测量,如果可以做到这个指标,那是真棒,但是现实情况是要把这个小量程放大到 ADC 的满幅度来完成高动态。

低量程如果前端有增益,后级 ADC/参考/数字链路噪声会被输入等效除以增益,所以主要矛盾会前移到放大器输入端之前。*

假设 100 mV 档采用 放大后进 ADC,则:

折算回输入端:

其中 包括放大器之后、ADC 输入、ADC 本身、参考耦合等后级噪声。

所以当 时:

这意味着后级噪声对输入端的贡献直接小 10 倍,一个比较严谨的说法是:

后级噪声折算到输入端要除以 10;所以如果后级输出端噪声是前级输入噪声的 10 倍,折算回来才等同。

也就是说,真正比较的是:

不是直接拿前后级原始噪声比。

举个数:

如果 ADC/后级在 ADC 输入端噪声是:

前端增益 ,折算到 100 mV 输入端就是:

如果前端输入端自身噪声是:

那后级仍然不可忽略,因为 50 nV 比 20 nV 大。 但如果后级是:

折算后:

那就确实基本不用太纠结后级了,应该稍微精确成:

时,后级噪声只有在端做到才不会拖后腿

不过在 DVM1107 这种低速 ΣΔ 架构里,后级 ADC 噪声通常确实不太可能是第一矛盾;现在来看对 100 mV 档,更合理的设计重点应该是:

也就是重压:输入端热电势,源阻抗热噪声,前端保护电阻热噪声,放大器输入电压噪声,放大器 0.1–10 Hz 噪声,输入偏置电流 × 源阻抗,继电器/开关漏电和热电势;而不是优先纠结 ADC 后端。

低量程靠增益吃满动态范围,系统噪声瓶颈会被推到放大器输入端之前。

放大器本身的输入噪声、1/f 噪声和热电势不属于后级,它们仍然是 100 mV 档的核心限制项。

关于满量程测量

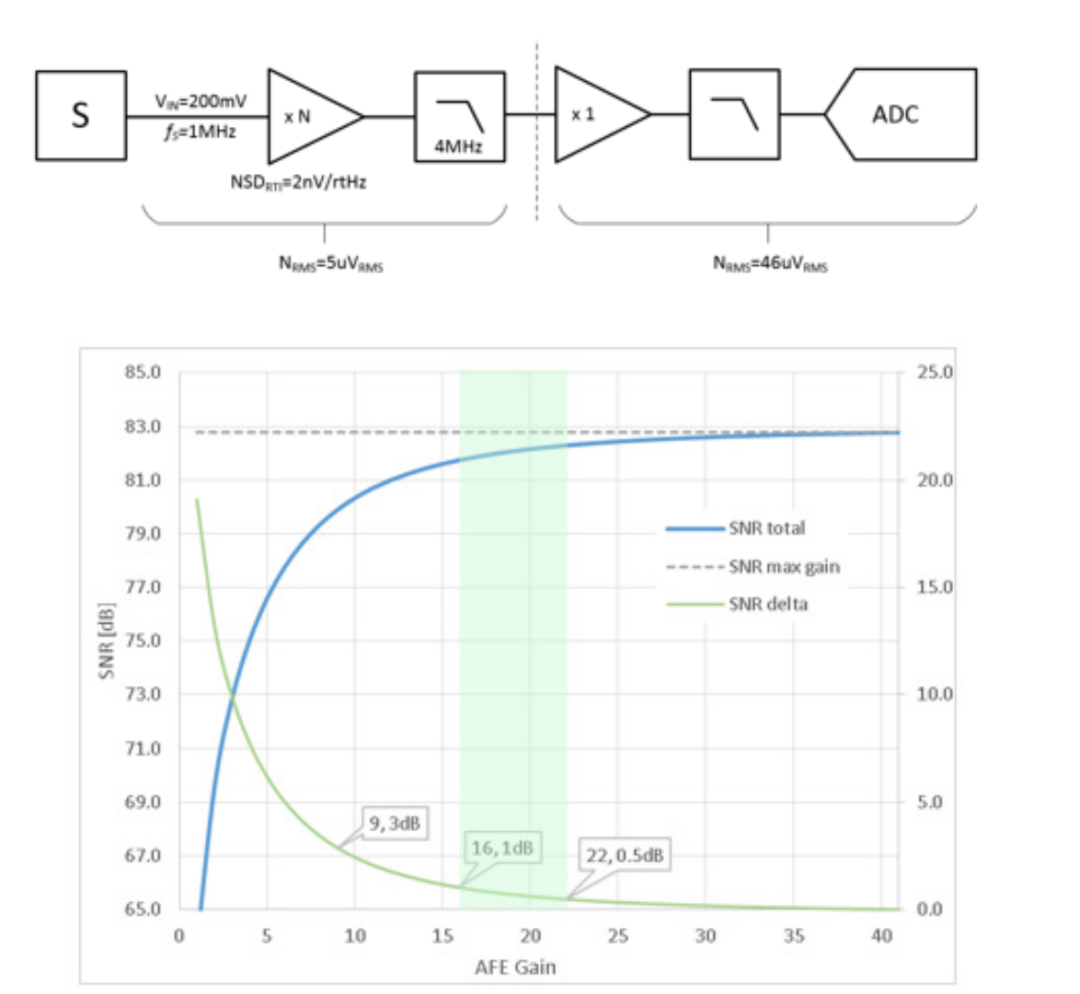

在 ADI 的这个文档里面就论述过这段

在 ADI 的这个文档里面就论述过这段

在之前的文章我也深度解读过,现在在 100mV 七位半的语境下再重看一遍。

精密信号链里,不能孤立看 ADC 噪声,也不能孤立看放大器噪声,而要看“各级噪声经过增益、带宽、折叠之后,最后谁主导”

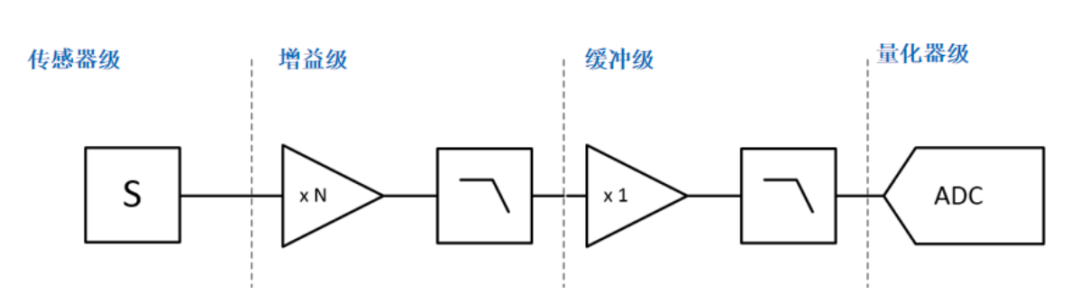

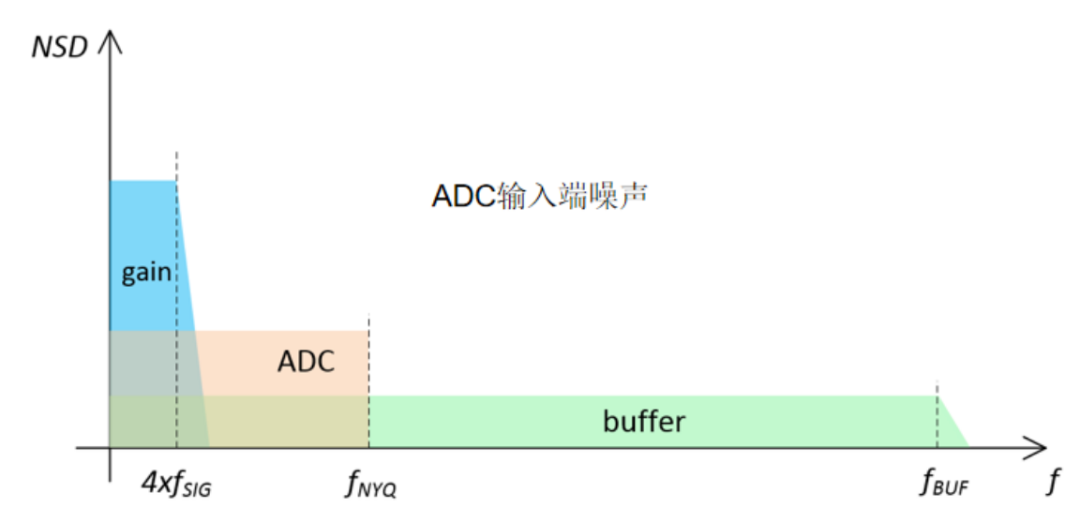

文章把典型数据采集链分成四级:传感器级 → 增益级 → 缓冲级 → 量化器/ADC 级;每一级都有自己的噪声谱密度和带宽,最后总噪声不是简单看谁的 nV/√Hz 小,而是要看:

也就是说,噪声谱密度 × 噪声带宽才决定最终 rms 噪声。

以上两个图就是在说明这个结构:增益级带宽较窄、缓冲级带宽很宽、ADC 噪声带宽由奈奎斯特频率决定;所有模拟前端噪声最后都会折算到 ADC 输入端。

文章说,小信号设计时,增益级的任务是把传感器小信号放大到 ADC 更合适的输入范围;这个逻辑和刚才说的 100 mV 档放大 10 倍进 ADC 是同一个思想。

但文章强调一个关键点:

增益放大信号的同时,也放大增益级输入端之前的噪声。

所以增益级输出端 SNR 与增益本身关系不大,因为信号和前级噪声一起乘以同一个 。文章明确说:噪声和信号以相同系数放大,因此增益级输出端 SNR 与增益系数无关。

数学上就是:

所以:

这解释了:前端增益不能改善放大器之前已经存在的 SNR,它只能降低后级噪声折算回输入端的影响。

为什么加增益后,后级噪声变得不重要?

如果增益级后面的缓冲器、ADC、参考输入等总噪声是 ,那么折算回增益级输入端是:

所以总输入等效噪声为:

如果 ,后级贡献输入等效直接除以 10。 如果 ,后级贡献输入等效除以 100。

这就是为什么低量程表通常会做前端增益:不是为了让前级噪声变小,而是为了让 ADC 后级噪声“不再主导”。

这篇文章第 4 页图 9 和图 10 也在表达类似观点:当输入幅度较小,例如 100 mV 级别时,信号链 SNR 往往由 AFE 主导;当信号幅度增大到一定程度后,才开始由 ADC 主导。

缓冲级不能随便去掉

文章第 3 页重点讲了“移除缓冲级”的后果;很多人会想:少一级缓冲,少一级噪声,岂不是更好?但文章结论相反:不建议实际设计中移除缓冲级。原因是 SAR ADC 采样时会产生反冲电荷,前级必须很快把 ADC 采样电容充到准确值。如果没有专门缓冲器,增益级就必须直接驱动 ADC,导致:

被迫从“信号所需带宽”扩展到“ADC 采样建立所需带宽”;文章例子里,移除缓冲级后,增益级噪声带宽从:

扩展到:

增加约 19 倍,总噪声从 68 μV rms 增加到 207 μV rms,SNR 从 92.6 dB 降到 82.9 dB。

这背后的通用原则是:

低噪声级不一定适合直接驱动 ADC;驱动能力和噪声优化经常是矛盾的。

但是 DVM1107 这类低速 ΣΔ 表来说,ADC 采样反冲不像高速 SAR 那么激烈,但道理仍然成立:前端增益级最好保持在低带宽、低噪声、低漂移状态;驱动 ADC/滤波/隔离最好交给后面的缓冲或 RC 网络。

带宽比噪声谱密度更容易有说法

文章第一页和第二页反复强调,缓冲级噪声谱密度可能很低,比如 1.5–5 nV/√Hz,但它的带宽可能远大于信号带宽,甚至是 ADC 噪声带宽的 10–15 倍。

这意味着:

看起来很好,但如果带宽是 100 MHz:

而另一个器件:

如果带宽只有 10 Hz:

反而小得多。

所以精密低频表里最重要的不是追求无限低的宽带噪声密度,而是:

把有效噪声带宽压到真正需要的范围

这和我们前面估计 DVM1107 在 10 PLC 下等效带宽约 2.5–3 Hz 是完全一致的;对 100 mV 档,真正要压的是 0.1–10 Hz 噪声、热电势、低频漂移,不是几十 MHz 的高速驱动噪声。(总之就是窄带测量对信号改善是巨大的,尽可能是缩小它)

数字滤波不是万能的

文章最后讲了一个很重要的限制:数字滤波可以滤掉带外噪声,但如果噪声已经在 ADC 采样过程中折叠进低频,就不能靠后面的数字滤波完全消除。

也就是:

采样前已经混叠/折叠进来的噪声,数字滤波救不回来。

比如有一个高频干扰通过前端非线性整流,变成低频漂移;或者 ADC 输入采样反冲把高频噪声折叠到低频,那么后面的 sinc 滤波器也不能把它当作“带外噪声”轻松拿掉;数字滤波只是最后一道“低通平均”,不是替代模拟前端的万能工具。

现在把这篇文章套回 DVM1107,如果 100 mV 档内部确实有前端增益,例如:

那么链路可以抽象为:

100 mV 输入

↓

输入保护 / 低热电势继电器 / RC

↓

低噪声低漂移增益级 G=10

↓

缓冲 / ADC输入网络

↓

LHA5658-2 ΣΔ ADC

↓

数字滤波 / PLC平均

那么总输入等效噪声是:

所以 100 mV 档的核心判断是:

只要增益够高,ADC 和后级噪声输入等效会被压下去;最后决定 100 mV 档表现的是输入端与增益级本身。

这和我讨论的想法完全一致;不过要特别注意: 放大器输入噪声不属于“后级噪声”。它是在增益之前产生的,不能被增益除掉,反而会和信号一起被放大。所以 100 mV 档真正要盯住的是:

(就是前面写的一切关于小信号的内容)这些才是低量程的主战场。

另外增益级不能为了驱动 ADC 被迫拓宽带宽;如果增益级既要低噪声,又要高速驱动采样电容,它的噪声带宽可能暴涨。文章第 3 页的例子就是这个:取消缓冲级后,增益级噪声带宽增加约 19 倍,SNR 下降约 10 dB。

所以正确策略不是“增益级直接硬怼 ADC”,而是:

低噪声增益级负责放大,缓冲负责驱动

预留一个小实验

如果你判断 DVM1107 的 100 mV 档(或者其它高位表)是不是内部做了合适增益,可以做一个实验:

先测 100 mV 档短路噪声,记录 10 PLC 下的标准差;再测 1 V 档短路噪声,同样 10 PLC;如果 100 mV 档是独立低噪声增益链路,那么它的输入等效噪声应该不会简单等比例变差;如果只是直接进 ADC 或简单分压/切档,噪声比例会不一样。

还可以看:

和

是否与量程规格中的标准差一致。DVM1107 规格表中 100 mV 档标准方差是 0.6 ppm,1 V 档是 0.15 ppm;换算到电压分别约 60 nV 和 150 nV。

这个现象反而说明低量程很可能确实经过了低噪声优化,因为 100 mV 档的绝对噪声并没有比 1 V 档更差。

总结

四条设计原则:

第一,增益级把后级噪声折算回输入端除以增益,所以低量程必须靠前端增益保护 ADC 动态范围。

第二,增益级不会改善它之前的 SNR,输入端噪声和放大器输入噪声是低量程的根本限制。

第三,不能随便移除缓冲级,因为增益级一旦被迫驱动 ADC,噪声带宽会大幅增加,SNR 反而变差。

第四,数字滤波只能去掉采样后仍在带外的噪声,已经折叠进低频的噪声救不回来。

对高位表的的 100 mV 档,最准确的设计理解是:

前端低噪声增益级决定低量程能力,和数字滤波决定后级读数稳定性。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-04-25,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录