FPGA相关职位笔/面试题分享(七)

FPGA相关职位笔/面试题分享(七)

FPGA技术江湖

发布于 2026-03-23 20:18:10

发布于 2026-03-23 20:18:10

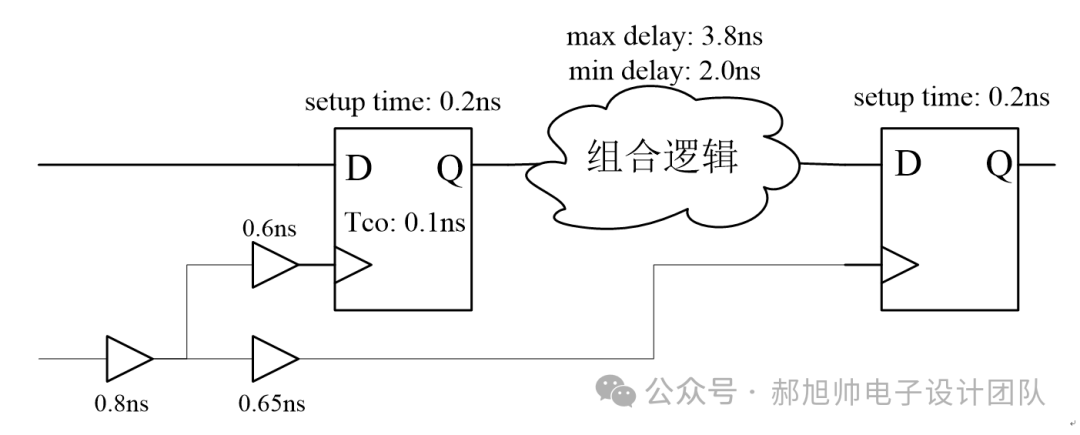

以下逻辑的时钟最快工作频率是多少?

解析:此类型题目考察点为基本的时序分析基础。

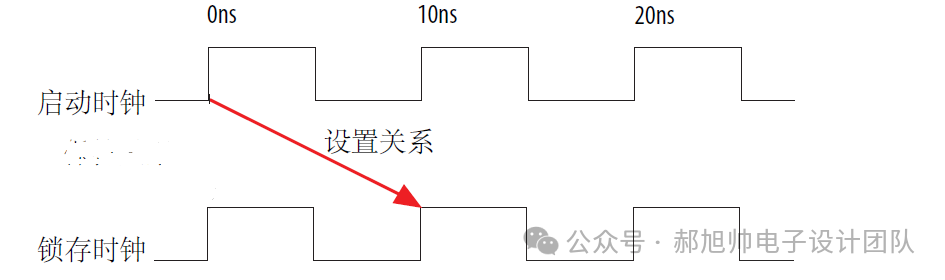

在时序逻辑电路中,无特殊说明时,前一级寄存器在第一个时钟边沿采样并发出数据,后一级寄存器在第二个时钟边沿采样前一级寄存器在第一个时钟边沿采样并发出的数据(该数据可能要经过一定的组合逻辑)。

我们通常把第一个时钟边沿称为发送沿(启动沿),第二个时钟边沿称为锁存沿。

只要能够保证在第二个寄存器在第二个时钟边沿采样时,由第一个寄存器在第一个时钟边沿采样并发出去的数据经过组合逻辑能达到就行(即:别耽误采样)。

所以呢,我们就能列出两个时间来:第一个是第二个寄存器在第二个时钟边沿采样的时间(建立时间检查中的要求时间),第二个是第一个寄存器在第一个时钟边沿采样经过组合逻辑达到第二个寄存器D端的时间(建立时间检查中的达到时间)。

由于两个寄存器是相同的时钟所驱动,故而两个时钟边沿相差一个时钟周期T。

我们可以将第一个时钟边沿的时间认为成0,第二个时钟边沿认为T。

时间计算都从最开始的时钟输入开始计算,时钟也是需要时间才可以走到寄存器的时钟端。

在计算中间组合逻辑延迟时,我们为了保证所有情况下都是对的,需要带入最大的延迟(此时达到时间最为悲观/最晚达到的情况下,还可以采样成功,那么其他情况就更能够成功了)。

寄存器能够稳定采样,要求数据D信号要在时钟端有采样沿之前的Setup 时间到达,否则无法稳定采样。

根据上述的题目中所给的时间可以计算得出:

要求时间= T + 0.8 + 0.65 - 0.2 = T + 1.25

达到时间 = 0 + 0.8 + 0.6 + 0.1 + 3.8 = 5.3

为了能够实现稳定采样,达到时间要早于要求时间所以:

T + 1.25 >5.3

即:T > 4.05 ns

计算得出最小的时钟周期,即可得出最大的时钟频率。

F = 1/T 约等于250Mhz。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-10-07,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读