混合信号PCB布局技巧

无论是传感器采集的微弱模拟信号,还是处理器高频切换的数字信号,一旦布局不当,就可能出现噪声耦合、信号完整性受损等问题,最终导致系统性能不达标。

混合信号 PCB 布局并非 “先放元件再布线” 的简单流程,而是需要从源头规划,电路板层决定信号回流路径,接地平面保障噪声隔离,电源与去耦技术则为系统稳定 “保驾护航”。

本文将按设计流程逐步展开,用通俗的技术语言与明确的实操规则,帮助读者建立系统化的布局思维。

1

元件放置:布局设计的 “地基工程”

元件放置是混合信号 PCB 设计的第一步,如同建房前的平面规划,直接决定后续布线难度与系统抗干扰能力。

核心原则是 “按模块分区、按信号路径布局”,既要避免高噪声元件干扰敏感电路,也要为后续布线预留合理空间。

整体布局逻辑

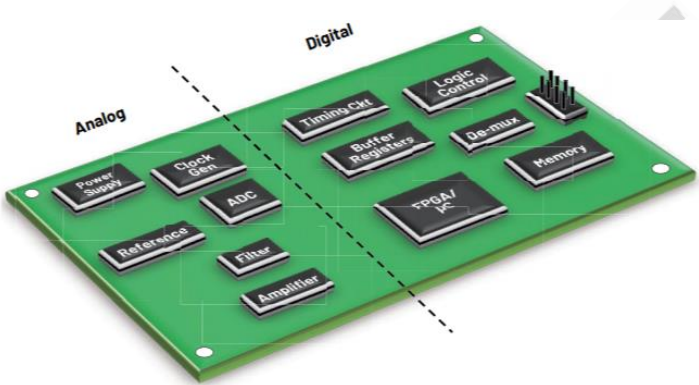

布局前需先梳理电路模块:将模拟模块(如传感器、放大器、ADC/DAC)、数字模块(如 MCU、FPGA、时钟电路)、电源模块(如 LDO、DC-DC)分开归类,确保同一功能的元件 “就近集中”。

例如,传感器与放大器应紧邻放置,减少模拟信号传输路径;处理器与内存颗粒需围绕 “信号最短路径” 布局,避免高频信号延迟。

同时,需提前规划布线通道:核心芯片(如 MCU)周围预留至少 2-3mm 的布线空间,模拟信号路径避免与数字信号交叉,高电流电源路径预留宽走线空间(通常≥1mm)。

关键元件的放置规则

(1)连接器:优先定位,靠边放置

所有连接器(如 USB、传感器接口)应优先放置在 PCB 边缘,既方便外接设备插拔,也避免占用板卡核心区域。

放置时需注意:ESD 保护元件(如 TVS 管)必须紧邻连接器引脚,距离≤5mm,确保静电快速泄放;若连接器同时传输模拟与数字信号(如带采样功能的接口),需在连接器附近划分 “过渡区”,避免信号直接交叉。

(2)热敏感元件:远离热源,单独分区

晶振、传感器等热敏感元件,需与功率器件(如 MOSFET、DC-DC 芯片)保持至少 3cm 间距,避免后者工作时的温升导致前者参数漂移(如晶振频率偏移)。

例如,51 单片机的 11.0592MHz 晶振,若靠近发热的线性稳压器,可能出现串口通信误码率升高的问题。

(3)混合信号器件:站在 “模拟与数字的边界”

ADC/DAC 是典型的混合信号器件,需放置在模拟区与数字区的交界处 —— 模拟引脚(如 AIN、AVDD、AGND)朝向模拟区,数字引脚(如 DOUT、DVDD、DGND)朝向数字区,避免引脚跨区导致的噪声耦合。

例如,12 位 ADC 芯片 ADS1115,其模拟输入端应紧邻放大器输出,数字输出端则靠近 MCU 的 SPI 接口,两者间距控制在 20mm 以内,减少信号传输损耗。

模拟与数字模块的隔离策略

模拟电路对噪声极为敏感(如微伏级的传感器信号),数字电路则会产生高频开关噪声(如 MCU 的 IO 口切换),因此必须在 PCB 上实现 “物理隔离”:

- 分区划分:建议将模拟区集中在 PCB 左侧,数字区在右侧,中间预留≥10mm 的隔离带(若数字电路频率≥100MHz,隔离带需扩大至 15mm);

- 元件归属:放大器、基准电压源(如 REF3030)、低噪声 LDO 等敏感元件,必须放在模拟区内;时钟发生器、逻辑门、高速接口芯片等高噪声元件,全部归入数字区;

- 跨区禁忌:数字信号线禁止穿入模拟区,模拟信号线也不得进入数字区,若必须交叉(如 ADC 的数字输出线),需在交叉处下方保留完整接地平面,减少耦合。

去耦电容与晶振的 “贴身布局”

(1)去耦电容:紧跟电源引脚,“越小越近”

去耦电容的核心作用是为芯片提供瞬时电流,抑制电源噪声,因此必须 “紧贴芯片电源引脚”:

- 小容值电容(0.01μF-0.1μF,陶瓷材质)距离引脚≤3mm,优先用 0402 封装,减少走线电感;

- 大容值电容(10μF-100μF,电解或钽电容)距离引脚≤25mm(约 1 英寸),用于滤除低频噪声;

- 若芯片有多个电源引脚(如 FPGA 的核电压与 IO 电压),每个引脚都需单独配置去耦电容,不可共用。

(2)晶振:独立区域,远离敏感电路

晶振是高频噪声源(如 8MHz 晶振的谐波可能达数百 MHz),布局时需注意:

- 晶振与芯片的时钟引脚距离≤10mm,负载电容(如 22pF)紧贴晶振两端,走线长度差异≤1mm,避免频率偏移;

- 晶振周围 300mil(约 7.62mm)范围内禁止放置模拟元件(如放大器、ADC),下方 PCB 层(包括顶层、底层、内层)需完全铺地,禁止布设任何信号线;

- 若板卡上有多个晶振(如 MCU 晶振与射频晶振),两者间距≥20mm,避免谐波相互干扰。

2

电源模块设计:系统稳定的 “能量保障”

电源是混合信号系统的 “心脏”,若电源噪声进入模拟电路,可能直接导致信号失真;若数字电源瞬态响应不足,则会引发处理器死机。

电源模块设计的核心是 “隔离、就近、低阻抗”,即模拟与数字电源分开,电源模块靠近负载,布线短而宽。

电源模块的隔离设计

模拟电源与数字电源必须独立供电,即使输入电压相同(如均为 3.3V),也需分开设计:

- 电源入口:若共用外部电源,需在入口处通过磁珠(如 100Ω/100MHz)或 0Ω 电阻分离,模拟侧接 LDO(如 AMS1117),数字侧接 DC-DC(如 MP1584),避免数字电源的开关噪声串入模拟侧;

- 电源平面:多层 PCB 中,模拟电源平面(如 AVDD)与数字电源平面(如 DVDD)需物理分割,边界与模拟 / 数字区对齐,平面铜箔厚度≥35μm(1oz),确保低阻抗(<50mΩ);

- 负载匹配:大电流数字负载(如 FPGA 核电压)的电源路径需单独规划,线宽≥2mm(载流 2A),远离模拟电源平面,避免电流变化导致的电压波动耦合。

电源布线的 “短直宽” 原则

电源布线的关键是减少电感与电阻:

- 短:电源模块到负载的距离≤50mm,例如 LDO 输出到 ADC 的 AVDD 引脚,走线长度越短,噪声损耗越少;

- 直:避免走折线或绕线,若必须拐弯,用 45° 角或圆弧过渡,减少信号反射;

- 宽:根据电流大小确定线宽,例如 1A 电流需≥1mm 线宽,2A 需≥2mm,大电流路径(如 DC-DC 输出)可采用铜皮填充,进一步降低阻抗。

ADC/DAC 的电源特殊优化

ADC/DAC 的电源噪声直接影响转换精度(1mV 噪声可导致 12 位 ADC 产生 0.5LSB 误差),需额外优化:

- 模拟电源(AVDD):单独从 LDO 引出,不与其他模拟元件共用路径,线上串联 10-100Ω 磁珠(根据噪声频率选择,如 100MHz 噪声用 100Ω 磁珠);

- 参考电压(VREF):布线最粗(≥0.3mm)、最短(<10mm),远离数字线与 DC-DC,专用滤波电容(100nF 陶瓷 + 10μF 钽电容)紧贴 VREF 引脚,接地仅连接 AGND;

- 电源滤波:在 ADC/DAC 的电源引脚处,采用 “100nF+1μF” 陶瓷电容并联,电容下方直接打地过孔,连接到模拟接地平面,减少接地电感。

3

去耦技术:电源完整性的 “降噪滤镜”

去耦技术的本质,是为电源噪声提供 “泄放通道”,确保芯片电源引脚的电压稳定。

要做好去耦,需先理解电源抑制比(PSRR)—— 该参数衡量芯片对电源噪声的抵抗能力,PSRR 越高,芯片受电源噪声影响越小。

但实际应用中,PSRR 会随频率升高而下降(如高性能放大器 OP1177 的 PSRR 在 1kHz 时为 120dB,1MHz 时降至 60dB),因此必须通过去耦电容补充抑制高频噪声。

去耦电容的选型搭配

不同电容的滤波频段不同,需组合使用才能覆盖宽频率范围:

- 低频去耦(<1kHz):用 10μF-100μF 电解电容或钽电容,作为瞬态电流的 “电荷库”,减少电源电压波动;

- 中频去耦(1kHz-100MHz):用 1μF-10μF 陶瓷电容(X7R 材质,温度稳定性好),滤除电源线上的开关噪声;

- 高频去耦(>100MHz):用 0.01μF-0.1μF 陶瓷电容(C0G 材质,高频特性优),紧贴芯片电源引脚,抑制高频谐波。

例如,MCU 的电源引脚旁,通常搭配 “10μF 钽电容 + 0.1μF 陶瓷电容”,前者应对电机启动等瞬态电流,后者滤除 IO 口切换产生的高频噪声。

去耦电容的布局要点

去耦电容的效果,80% 取决于放置位置,核心规则是 “最短路径、低电感连接”:

- 紧贴引脚:小容值电容(如 0.1μF)距离芯片电源引脚≤3mm,大容值电容(如 10μF)≤25mm,避免长走线引入电感;

- 接地优先:电容的接地端需直接连接到接地平面,优先通过 “T 型连接” 或过孔直达地平面,不绕经其他元件;

- 避免共享:每个芯片的去耦电容独立配置,不可多个芯片共用一组电容,尤其模拟芯片与数字芯片,需各自单独去耦。

特殊场景的去耦方案

若板卡存在强噪声源(如射频模块、大功率电机驱动),需在基础去耦上增加措施:

- 电源入口:加 π 型滤波器(电感 + 两个电容),电感值 10-100μH,电容用 10μF+0.1μF,抑制外部噪声传入;

- 高频噪声隔离:在模拟电源线上串联铁氧体磁珠(如 BLM18PG102SN1),磁珠阻抗在噪声频率下≥100Ω,阻断高频噪声进入模拟电路;

- 大面积铺铜:未使用的 PCB 区域铺接地铜皮,与去耦电容的接地端连接,形成 “噪声吸收区”,减少 EMI 辐射。

4

电路板层设计:信号回流的 “通道规划”

完成元件放置后,需先确定电路板层数与层结构,再进行布线 —— 层结构决定了信号的回流路径,若设计不当,可能导致接地阻抗升高、信号串扰加剧。

对于混合信号 PCB,四层板是性价比最高的选择,既能满足隔离需求,又不会过度增加成本;若系统复杂度高(如多 ADC、高频数字电路),则需升级为六层板。

典型四层板的层结构设计

四层板的经典结构为 “信号 - 地 - 电源 - 信号”,各层功能明确,抗干扰能力强,具体配置如下:

这种结构的优势在于:接地层与电源层相邻,形成天然的 “平面电容”(FR4 材质下,4-6mil 间距的平面电容约 75pF / 平方英寸),可辅助滤除高频电源噪声;顶层模拟信号以接地层为参考,底层数字信号以电源层为参考,两者通过接地层隔离,减少交叉干扰。

层设计的关键注意事项

- 平面完整性:接地层与电源层尽量保持完整,避免大面积挖空(如为避让过孔而切断平面),尤其是模拟接地层,断裂会导致接地阻抗升高,噪声无法有效泄放;

- 层间对齐:电源层的分割边界需与接地层的模拟 / 数字分区对齐,例如模拟电源区下方必须是模拟接地层,避免 “电源 - 接地” 跨区导致的噪声耦合;

- 过孔连接:多层板的接地平面需通过 “过孔阵列” 连接(如每 20mm 打一个地过孔),确保各层接地阻抗一致,高频噪声可跨层泄放。

5

接地平面设计:噪声隔离的 “核心防线”

接地是混合信号 PCB 设计中最易出错的环节,也是影响系统性能的关键。

很多初级工程师会陷入 “必须分割模拟地与数字地” 的误区,实际上,接地平面的设计需根据系统复杂度选择 —— 简单系统用单一接地平面更优,复杂系统才需分割,核心目标是 “让所有返回电流有低阻抗路径,且不干扰敏感电路”。

单一接地平面:简单系统的优选

若系统仅含 1-2 个低电流 ADC/DAC(如 8 位 ADC、电流<10mA),单一完整接地平面是最佳选择,优势在于:

- 低阻抗:完整铜箔的接地阻抗远低于分割平面,返回电流可沿最短路径流动,减少地弹噪声;

- 易布线:无需考虑平面分割边界,信号线可自由规划,降低设计难度;

- 抗干扰:完整接地平面可屏蔽外部 EMI,同时减少内部信号辐射。

- 设计要点:

- 分区规划:在接地平面上通过元件布局划分 “模拟区” 与 “数字区”,模拟元件下方的接地铜箔保持完整,数字元件的返回电流不流经模拟区;

- 信号控制:数字信号线仅在数字区布线,模拟信号线仅在模拟区布线,避免跨区导致返回电流路径变长;

- 单点接地:电源地、模拟地、数字地在电源入口处单点连接(如通过 0Ω 电阻),确保整个系统接地电位一致。

模拟地与数字地分离:复杂系统的解决方案

当系统含多个高电流 ADC/DAC(如 16 位 ADC、电流>50mA)或高频数字电路(如 100MHz 以上时钟)时,单一接地平面可能无法隔离噪声,需采用分离接地平面:

- 平面分割:在接地层将 AGND 与 DGND 物理分离,间隙≥1mm,分割边界与模拟 / 数字区对齐;

- 单点连接:AGND 与 DGND 仅在一点连接,优先选择 ADC/DAC 下方或电源入口处,通过磁珠(100Ω/100MHz)或 0Ω 电阻连接,避免形成环流;

- 元件归属:模拟元件(放大器、传感器)的接地引脚仅连接 AGND,数字元件(MCU、逻辑门)仅连接 DGND,混合信号元件(ADC/DAC)的 AGND 引脚接 AGND 平面,DGND 引脚接 DGND 平面,通过内部单点连接。

例如,多通道数据采集卡中,4 个 16 位 ADC 的 AGND 全部连接到 AGND 平面,FPGA 的 DGND 连接到 DGND 平面,两者在电源入口处通过 0Ω 电阻单点连接,既隔离数字噪声,又确保接地电位一致。

接地设计的必查清单

无论采用哪种接地方案,布局完成后需按以下清单验证:

- 所有芯片的接地引脚是否直接连接到对应接地平面,无长走线(≤5mm);

- 接地平面是否完整,无大面积断裂(尤其是模拟区下方);

- 数字信号线是否跨越 AGND 与 DGND 的分割边界(禁止跨越,否则返回电流路径不连续);

- 混合信号元件(ADC/DAC)的 AGND 与 DGND 是否按 datasheet 要求连接,有无错接;

- 接地过孔是否充足,多层板的接地平面是否通过过孔阵列连接(每 20mm 至少 1 个过孔);

- 未使用的 PCB 区域是否铺地,且与对应接地平面连接,无悬空铜皮。

混合信号 PCB 布局设计,是 “规则 + 经验” 的结合 —— 掌握元件放置的分区逻辑、电源去耦的频率匹配、电路板层的路径规划、接地平面的隔离技巧,就能避开 80% 的常见问题。

对于初级工程师而言,无需追求复杂的优化方案,先落实基础准则:

- 元件放置:模拟与数字分区,敏感元件远离噪声源;

- 电源设计:模拟与数字电源分离,布线短直宽;

- 去耦电容:紧贴引脚,高低频搭配;

- 电路板层:四层板优先选 “信号 - 地 - 电源 - 信号”;

- 接地平面:简单系统用单一平面,复杂系统单点分离。

实际设计中,可结合本文准则逐步验证:先规划模块分区,再放置关键元件,接着确定层结构,最后布线与接地优化。

遇到噪声问题时,优先检查接地是否完整、去耦电容是否到位 —— 多数情况下,这些基础环节的优化,就能显著提升系统性能。

随着设计经验积累,可进一步学习高频信号完整性、EMC 优化等进阶知识,但扎实的基础布局能力,始终是混合信号 PCB 设计的核心竞争力。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-11-29,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录