Micron:SSD性能、容量与IO架构的未来

Micron:SSD性能、容量与IO架构的未来

数据存储前沿技术

发布于 2026-03-09 17:46:42

发布于 2026-03-09 17:46:42

阅读收获

- 深入理解AI工作负载下SSD性能瓶颈的端到端视角,区分主机与设备端限制,为系统优化提供方向。

- 掌握PCIe带宽折损、小包IOPS极限及容量-性能耦合等物理层挑战,指导存储产品选型与架构设计。

- 洞察GPU作为IO发起引擎的趋势,以及计算型存储、DPU等新架构在提升AI集群效率中的关键价值。

- 认识到IOPS/Watt在AI数据中心中的决定性作用,为评估存储方案的TCO提供重要依据。

全文概览

AI浪潮席卷全球,数据洪流对存储系统提出前所未有的挑战。传统SSD架构在面对高并发、小包IOPS时,性能瓶颈日益凸显。是接口带宽不足?还是控制器算力受限?抑或是功耗墙和容量-性能耦合的物理极限?本文将深入剖析AI时代SSD的端到端性能瓶颈,并探讨从CPU到GPU的IO发起权转移,以及计算型存储等前瞻性架构如何重塑未来存储格局。你是否已准备好迎接这场存储革命?

👉 划线高亮 观点批注

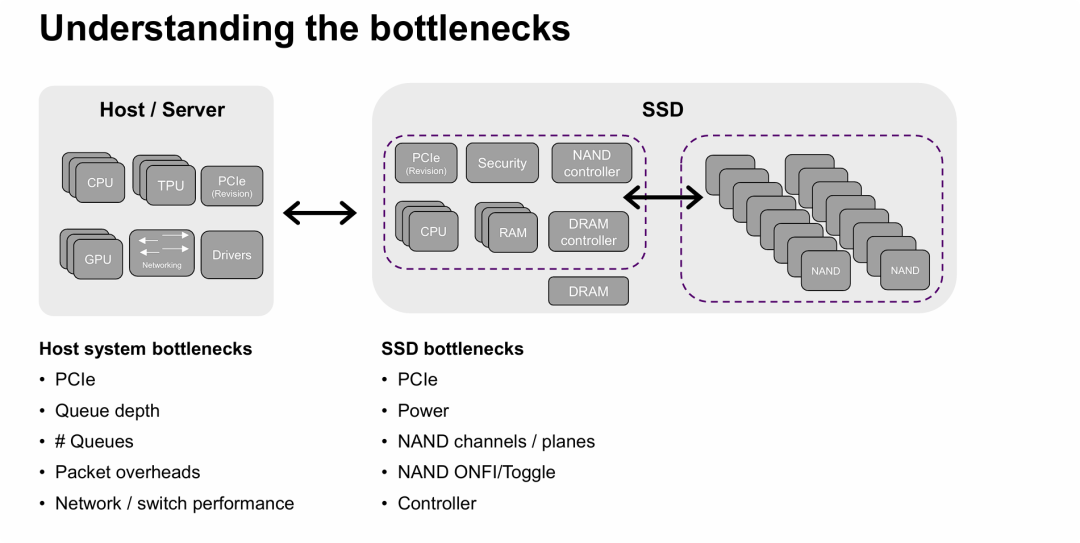

图片的核心观点是端到端的存储性能分析视角。它强调了存储性能不仅仅取决于SSD本身,而是受限于从主机应用到NAND介质这一长链路中的任何一个环节(木桶效应)。

- 瓶颈的二元分布:明确区分了主机端瓶颈(软件栈、队列机制、网络)和设备端瓶颈(介质物理特性、内部架构、功耗)。

- 内部架构的复杂性:SSD不再被视为一个黑盒,而被拆解为控制器算力、DRAM带宽、NAND接口速率(ONFI/Toggle)和并行度(Channels/Planes)等多个潜在的性能制约点。

- AI/HPC场景暗示:主机端列出的GPU和TPU表明,这可能是在高并发、高吞吐量的AI训练或推理场景下对存储瓶颈的分析,这类场景对Queue Depth和PCIe带宽尤为敏感。

瓶颈类型 | 描述 |

|---|---|

Host系统瓶颈 | |

PCIe | PCIe总线的带宽限制或延迟。 |

Queue depth | I/O请求队列的深度是否足以填满存储设备的并发能力,或者过深导致延迟。 |

Queues | NVMe协议支持多队列,队列数量不足可能限制多核CPU的性能发挥。 |

Packet overheads | 协议栈处理数据包带来的CPU和延迟开销。 |

Network / switch performance | 在网络存储(如NVMe-oF)场景下,网络带宽和交换机转发能力构成的瓶颈。 |

SSD内部瓶颈 | |

PCIe | SSD接口端的物理速率限制(如x4通道的带宽上限)。 |

Power | 功耗墙或热设计功耗(TDP)限制了SSD的最高性能持续输出。 |

NAND channels / planes | 控制器与NAND颗粒之间的并行度限制。通道数越少,并发读写能力越弱。 |

NAND ONFI/Toggle | NAND闪存接口标准(如ONFI或Toggle DDR)的传输速率限制(例如从NAND颗粒传输数据到控制器的速度)。 |

Controller | 主控芯片的算力瓶颈,处理FTL(闪存转换层)、垃圾回收(GC)或纠错(ECC)时的处理能力不足。 |

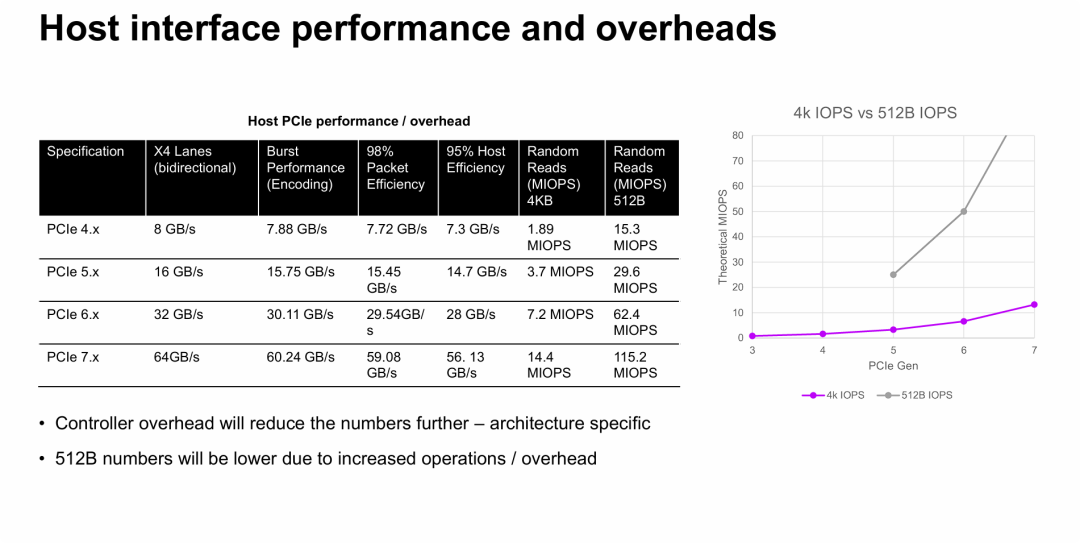

左侧表格是单盘SSD,PCIe4通道带宽和性能理论测算。

图片的核心观点是 “接口带宽不等于实际性能,且小包IOPS面临物理极限挑战”。

- 带宽折损是必然的:从物理层(PHY)到应用层,带宽会经历编码(Encoding)、协议包头(Packet)和主机效率(Host Efficiency)的三重折损。PCIe 7.0 宣称的 64GB/s,实际可用约为 56GB/s(约 12.5% 的损耗)。

- PCIe 7.0 的性能飞跃:每一代 PCIe 标准都带来了带宽的翻倍,进而推动了理论 IOPS 上限的翻倍。

- 小包(512B)的性能陷阱:虽然理论上小数据块利用 PCIe 7.0 带宽可以达到惊人的 1.15 亿 IOPS,但这在工程上极难实现。这揭示了未来存储系统的核心瓶颈将从 “带宽限制” 转移到 “包处理率(PPS)限制”——即主机 CPU 或 SSD 控制器无法在每秒内处理如此海量的微小 I/O 请求。

===

维度 | 对比项 | Host CPU (通用计算) | SSD Controller (近数据计算) |

|---|---|---|---|

资源消耗 | 核心优势 | 极强的通用算力,适合复杂逻辑 | 极高的能效比 (IOPS/Watt),卸载 Host 负担 |

主要瓶颈 | 中断风暴、上下文切换、核心成本昂贵 | 算力上限低、DRAM 容量小、散热受限 | |

最佳场景 | 复杂事务处理、操作系统管理、全局调度 | 数据压缩、透明加密、简单过滤 (Push-down) | |

数据重力 | 数据移动 | 高 (需将所有数据搬运至内存) | 低 (仅传输结果,数据在本地处理) |

带宽压力 | 极易占满 PCIe 带宽,尤其在全表扫描时 | 显著降低 PCIe 拥塞,释放带宽给关键业务 | |

延迟特性 | 受总线和内核协议栈影响,长尾延迟不可控 | 内部硬件直通,延迟更低且稳定 |

图中提到的 512B 小包 IOPS 爆炸 问题,目前的解决思路并非单一选择,而是融合:

- DPU / SmartNIC 的崛起:在 Host 和 SSD 之间引入 DPU,专门负责卸载网络和存储协议栈(如 NVMe-oF, TCP/IP),把 Host CPU 从繁重的 I/O 中断中解放出来。

- 计算型存储(Computational Storage):将简单的过滤(Filter)、扫描(Scan)、压缩任务下沉到 SSD 控制器,顺应数据重力。

- Host 侧软件优化:放弃传统的中断模式,全面转向 SPDK 或 io_uring 这种轮询(Polling)模式,以 100% 占用某些 CPU 核心为代价,换取无锁、零上下文切换的极致 IOPS 处理能力。

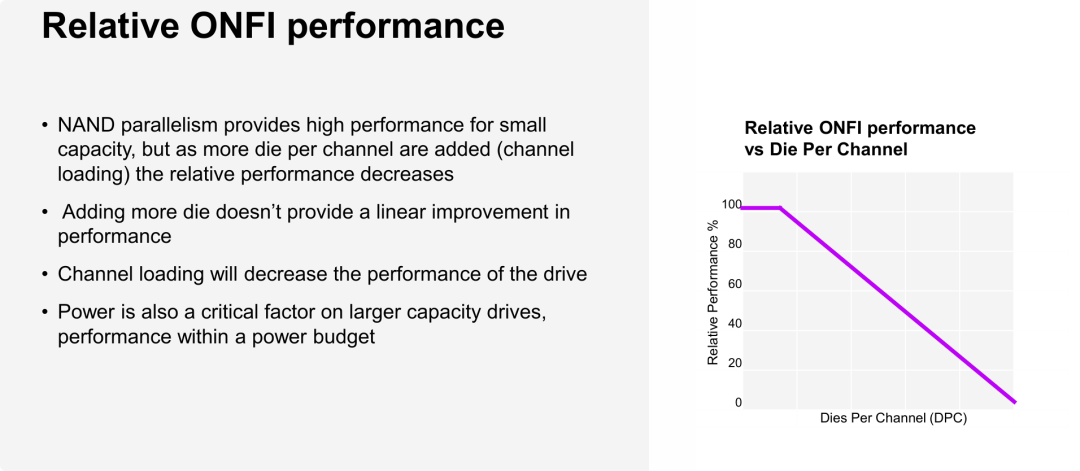

图片的核心观点揭示了大容量SSD设计的物理层瓶颈——“电容负载效应”。

- 信号完整性(Signal Integrity)瓶颈:ONFI总线是共享总线架构。当一个通道上挂载太多的Die(高DPC),总线上的寄生电容会增加。为了保证信号的准确读取,控制器必须降低ONFI接口的时钟频率(例如从 2400 MT/s 降级到 1600 MT/s 甚至更低)。

- “容量”与“速度”的权衡:为了追求大容量(增加Die数量),往往不得不牺牲接口速度。这就是为什么某些极大容量的企业级SSD,其随机读写延迟或突发带宽反而不如中等容量版本的原因。

- 功耗墙限制:除了信号问题,同时激活过多的Die会瞬间突破SSD的TDP(热设计功耗),迫使固件进行热节流(Throttling),进一步限制了性能发挥。

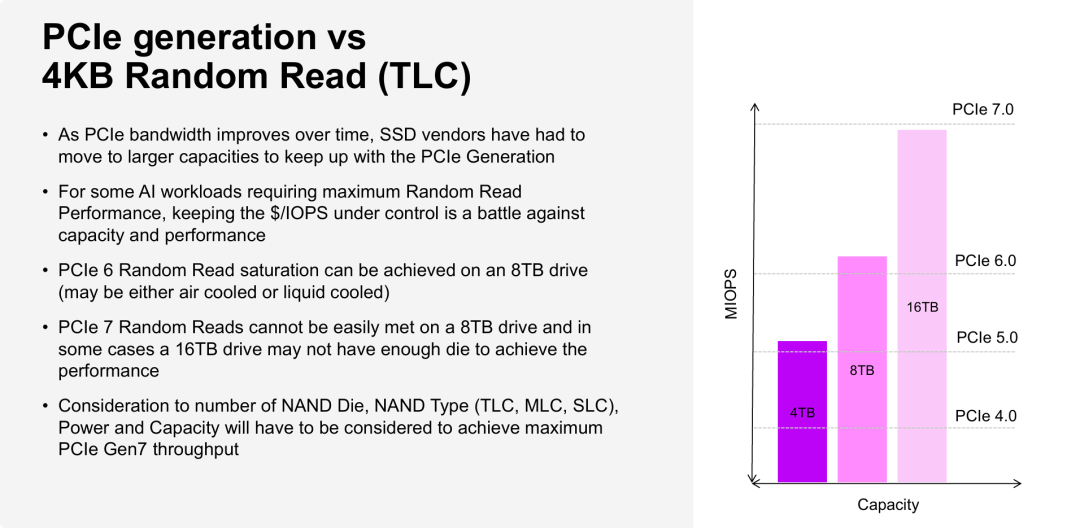

张图片的核心观点是 "性能与容量的强制绑定"(Performance-Capacity Coupling)。

- "小盘无高性能":在 PCIe 6.0/7.0 时代,你无法买到一个高性能的 4TB 硬盘。物理限制决定了,要实现每秒上亿次的 IOPS,必须有足够多的 NAND 颗粒同时工作,这强制要求 SSD 的容量必须很大(16TB+)。

- 并行度税(Parallelism Tax):为了获得接口承诺的带宽,用户被迫为“不需要的存储容量”买单。这极大地影响了 AI 集群的 TCO(总拥有成本)。

- 技术天花板:TLC 介质在 PCIe 7.0 时代面临巨大挑战,单靠堆容量已显吃力,暗示未来可能需要更快的介质(如 XL-Flash, SLC 模式)或新的架构突破。

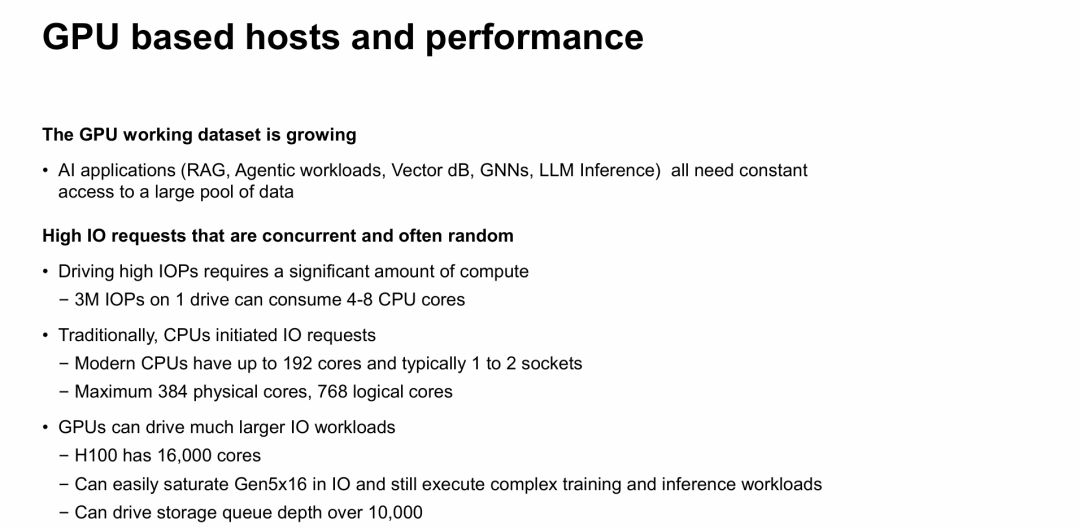

图片的核心观点是 "I/O发起权的转移"(Offloading I/O Initiation to GPU)。

- CPU的I/O瓶颈不在带宽,而在算力:驱动数百万IOPS会消耗大量CPU核心(4-8核/3M IOPS)。在AI集群中,CPU核心应当用于调度和逻辑控制,而不是被I/O中断处理耗尽。

- GPU更适合做大规模并行I/O:凭借上万个核心和对超高队列深度(QD > 10,000)的容忍度,GPU天生适合处理AI场景下的大规模、高并发、随机读取任务。

- 架构暗示:这暗示了存储技术栈必须变革,从传统的 "CPU读取 -> 内存 -> 拷贝至GPU" 模式,转向 GPU直接读取存储(如 GPUDirect Storage / GDS) 的模式,以释放CPU并跑满Gen5/Gen6带宽。

Nvidia GPU作为IO发起引擎的技术实现

- 主要内容:该文章介绍了NVIDIA提出的BaM(GPU直接访问NVMe设备)架构,通过将GPU转变为数据访问引擎,解决了大规模数据集无法放入内存的问题。BaM架构允许GPU直接访问NVMe SSD,绕过CPU调度,显著提升了存储带宽和性能。文章还探讨了GPU和NVMe之间的瓶颈,强调了需要更多高速存储设备来支持高性能数据访问,并提出了通过GPU初始化的动态请求和高效的NVMe存储技术来实现更高数据吞吐量和更低成本效益的方法。

2. Nvidia SCADA:GPU如何驾驭数据,突破内存墙?

- 主要内容:该文章讨论了Nvidia的SCADA技术,提出将GPU转变为“编排器”,使其掌握数据控制权,并直接按需访问分层存储。文章诊断了当前以CPU为中心的数据加载架构的效率问题,提出必须反思加速器-数据接口,实现控制权的反转,让GPU直接按需访问存储,从而隐藏I/O延迟。文章还强调了软件栈和存储I/O路径是新的瓶颈,GPU的并行架构有能力发出海量并发I/O请求,但当前的软件栈习惯于串行化或批处理I/O,限制了系统性能。

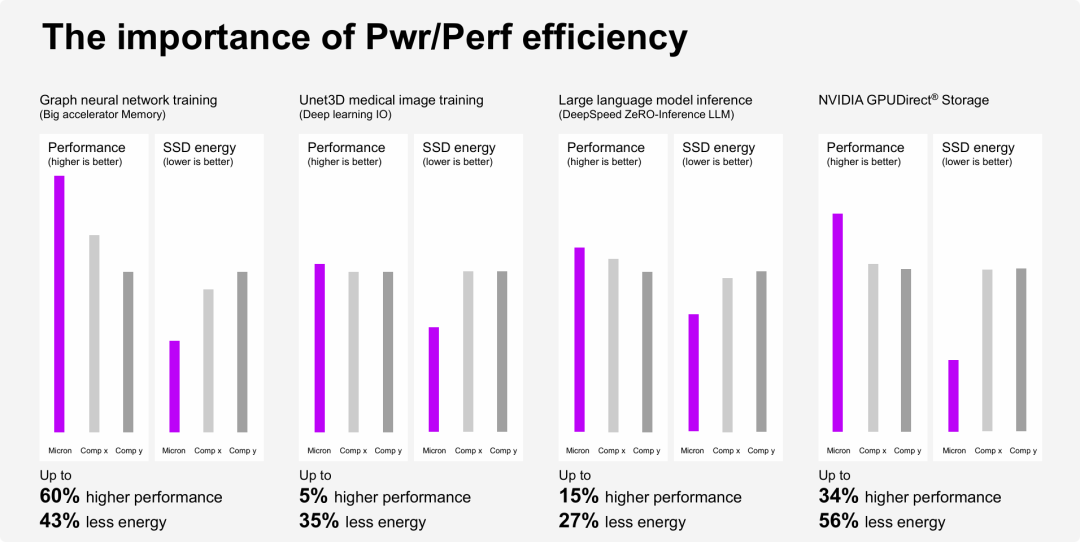

图片的核心观点是 "高性能必须伴随高能效(IOPS/Watt 是关键指标)"。

- 能效比决定AI集群规模:在AI数据中心,电力是稀缺资源。图表强调的不仅仅是“跑得快”(Performance),更是“吃得少”(Energy)。Micron 试图证明其 SSD 能够在相同的电力预算下提供更高的算力支持,或者在同等算力下节省大量电力。

- 实际AI工作负载的验证:不同于简单的跑分软件(如FIO),这里列举的 GNN、Unet3D、DeepSpeed 和 GDS 都是真实的、前沿的 AI 生产环境负载。这表明 SSD 的固件和架构针对随机小IO(GNN/GDS常见特征)和混合读写进行了专门优化。

- GDS与BaM的优势:特别是在 GPUDirect Storage 和 BaM 这种绕过 CPU、对存储延迟和吞吐极其敏感的场景下,Micron 显示出巨大的优势(性能+34% / +60%),暗示其控制器在处理 高并发、低延迟 请求方面具有独特的架构优势。

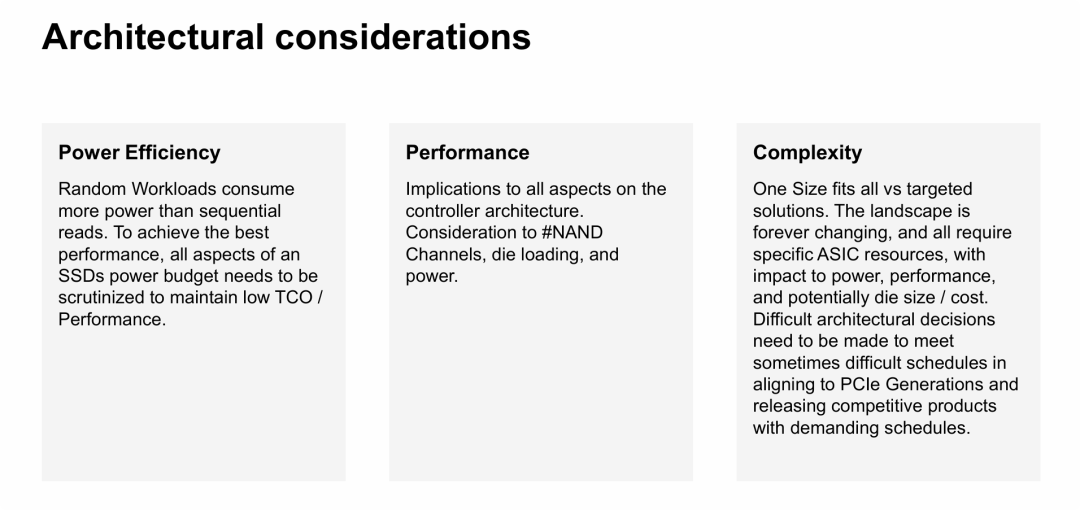

图片的核心观点是 "高性能SSD设计的‘不可能三角’"。

- 设计复杂度的爆炸:SSD设计已不再是简单的堆砌闪存。在PCIe Gen5/6/7时代,架构师必须在有限的 功耗预算(Power Budget)、严苛的 ASIC成本/尺寸 和 上市时间(Time-to-Market) 之间做极其艰难的取舍。

- “通用存储”的终结:图片暗示了市场趋势正在转向 "Targeted Solutions"。由于随机负载(Random Workloads)的高能耗特性,面向AI(高随机)和面向大数据归档(高顺序)的SSD架构将彻底分道扬镳。

- 系统工程视角:高性能是控制器架构、NAND物理特性(通道/负载)和固件算法综合作用的结果,任何一个短板(比如为了省电削减了ASIC资源)都会导致产品失败。

延伸思考

这次分享的内容就到这里了,或许以下几个问题,能够启发你更多的思考,欢迎留言,说说你的想法~

- GPU Direct Storage和计算型存储等技术,在实际部署中会面临哪些生态系统兼容性、开发难度和成本挑战?

- 随着NAND技术和PCIe标准的演进,SSD的“不可能三角”将如何被打破或重新定义?未来是否会出现针对特定AI工作负载的极致定制化存储?

- 在追求极致性能和能效比的同时,数据可靠性、持久性以及存储管理复杂性将如何平衡和演进?

原文标题:Future architectures for AI workloads[1]

Notice:Human's prompt, Datasets by Gemini-3-Pro

#FMS25 #GPU存储IO优化

---【本文完】---

丰子恺-护生画集-平等

👇阅读原文,搜索🔍更多历史文章。

- https://files.futurememorystorage.com/proceedings/2025/20250805_SSDT-102-1_Sykes-FINAL-FINAL.pdf ↩

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-02-08,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读