Micron:U.2的黄昏:PCIe 6.0时代为何独宠EDSFF?

Micron:U.2的黄昏:PCIe 6.0时代为何独宠EDSFF?

数据存储前沿技术

发布于 2026-03-09 17:32:48

发布于 2026-03-09 17:32:48

阅读收获

- 洞悉物理瓶颈:深入理解为何在PCIe 6.0的严苛要求下,U.2接口在信号损耗、回波反射和电气串扰方面已达物理极限,帮助你在下一代服务器系统设计中规避关键风险。

- 掌握设计精髓:明确EDSFF标准如何通过金手指设计、引脚背面隔离以及灵活的1连接器拓扑,从根本上解决高速信号完整性问题,为优化系统链路预算提供具体的技术路径。

- 评估TCO优势:从散热效率角度,量化对比EDSFF(E3.S)与U.2在降低服务器风扇功耗和冷却成本方面的显著优势,为数据中心总体拥有成本(TCO)分析提供关键决策依据。

全文概览

在数据中心存储领域,U.2接口凭借其长达15年的市场主导地位,已成为企业级SSD的代名词。然而,随着PCIe 6.0时代(64 GT/s)的到来,数据传输速率的翻倍不仅带来了性能的飞跃,也对物理链路提出了前所未有的信号完整性挑战。总损耗预算从36dB压缩至32dB,这意味着信号在传输路径上几乎没有容错空间。

我们不禁要问:这位久经沙场的“老将”U.2,其源自SAS时代的物理结构,还能否驾驭PCIe 6.0这匹“烈马”?当信号反射、电气串扰和散热成为不可逾越的物理障碍时,行业又将目光投向了何方?本文将深入剖析U.2在高速信号下的物理瓶颈,并揭示为何更新的EDSFF标准,凭借其在拓扑结构、引脚设计和散热效率上的根本性优势,已不再是一个可选项,而是通往PCIe 6.0及未来高速存储时代的必然选择。

👉 划线高亮 观点批注

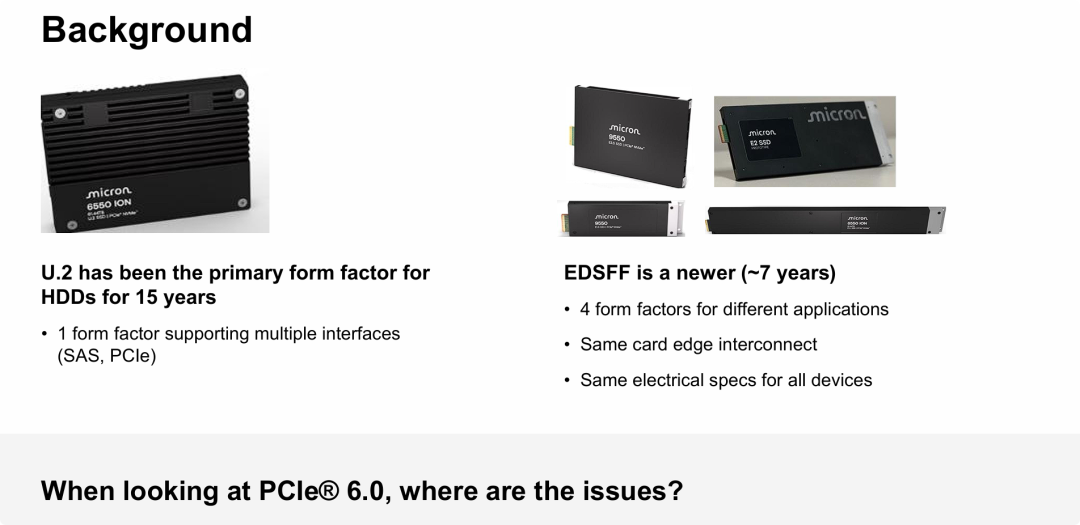

图片主要对比了存储行业从传统的 U.2 外形尺寸向更现代的 EDSFF 标准的演进。

- U.2 的局限与历史: U.2 虽然兼容性强且历史悠久,但在应对高性能需求时可能已显疲态。

- EDSFF 的优势: 作为新标准,EDSFF 通过统一的电气规范和金手指设计,提供了更灵活的形态选择,旨在优化数据中心的空间利用率和散热效率。

- 引出性能瓶颈: 幻灯片最后抛出了关于 PCIe 6.0 适配性的疑问,旨在引导观众思考在超高速总线时代,这些物理结构是否会成为限制存储性能发挥的“瓶颈”。

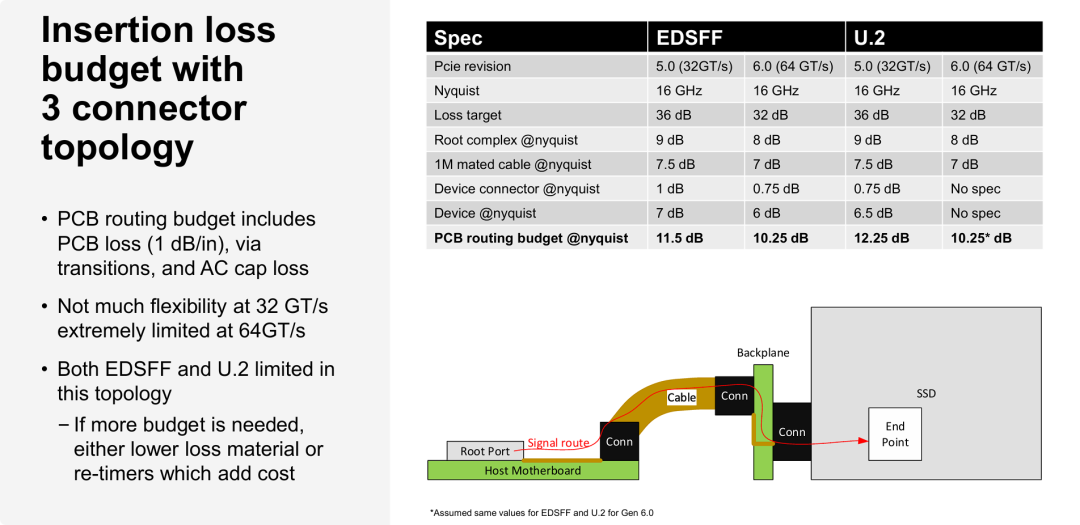

图片展示了随着总线速度提升至 PCIe 6.0 (64 GT/s),信号完整性设计的严峻性:

- 物理极限挑战:由于 PCIe 6.0 的总损耗预算从 36 dB 压缩至 32 dB,留给 PCB 布线的空间变得非常局促(仅约 10.25 dB)。

- U.2 标准的缺失:表格显示 U.2 在 PCIe 6.0 下缺乏明确的设备级连接器规范(No spec),反映了传统 U.2 接口在超高速传输中的滞后性。

- 成本权衡:在三连接器(图中所示)的复杂拓扑中,为了抵消链路损耗,厂商不得不考虑昂贵的重定时器或更高等级的 PCB 材料,这直接增加了系统的硬件成本。

Question

如何理解这里的损耗dB和PCB布线空间的关系?

在高速信号传输中,dB(分贝) 是衡量信号强度衰减的单位。您可以将其理解为信号的“路费预算”:

- 损耗预算(Loss Budget)是有限的:图片显示 PCIe 6.0 的总损耗目标从 36 dB 压缩到了 32 dB。这意味着信号从发送端到接收端,允许“挥霍”的能量变少了。

- PCB 布线是“耗能大户”:图片提到 PCB 的损耗率约为 1 dB/英寸。

- 计算逻辑:

- 总预算(32 dB)减去固定资产损耗(如根端口、线缆、连接器、SSD 内部损耗等),剩下的才是留给 PCB 布线的“余额”。

- 布线空间压缩:在 PCIe 6.0 下,EDSFF 的 PCB 布线预算仅剩 10.25 dB。按照 1 dB/英寸计算,这意味着从主板到接口的物理走线长度不能超过 10.25 英寸(约 26 厘米)。

- 连锁反应:如果主板很大,走线必须很长(超过预算),信号就会因为衰减太严重而无法识别。此时就必须花费额外成本去购买更贵的低损耗 PCB 材料(降低每英寸的 dB 损耗)或者加装 Re-timer(重定时器) 芯片来像“中继站”一样放大信号。

U.2 缺乏设备级连接器规范,是否就意味着,PCIe Gen6 就不能兼容了?

- 并不是物理上绝对不能插:如果厂商强行在 U.2 形状的硬盘上跑 PCIe 6.0,理论上可以尝试,但因为没有“官方规范”指导,兼容性和稳定性将极差。

- 行业重心转移:图片对比 U.2 和 EDSFF 的目的就是告诉你,EDSFF 才是 PCIe 6.0 的正统续作。EDSFF 拥有明确的 6.0 规范(Device connector 损耗定为 0.75 dB),而 U.2 则被留在了 5.0 时代。

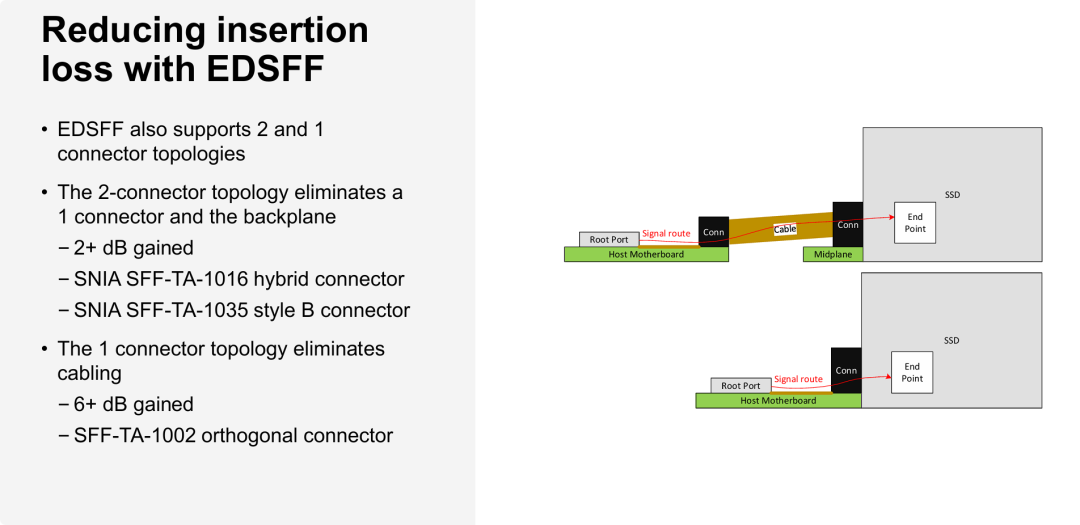

图片给出了解决 PCIe 6.0 信号损耗预算紧张的具体“减法”方案:

- 链路扁平化:通过减少连接器数量和消除电缆,可以有效回收损耗预算。尤其是 1 连接器拓扑(图下),通过消除电缆能节省 6dB 以上的预算,这对只有 32dB 总预算的 PCIe 6.0 来说至关重要。

- 标准化支撑:EDSFF 的优势在于其配套的多种连接器标准(如 SFF-TA-1002/1016/1035),允许设计者根据服务器机箱空间灵活选择“高性能(短路径)”或“高密度(带线缆)”的设计。

- 技术路径清障:由于 U.2 难以实现这些灵活的扁平化拓扑组合,这张图进一步证明了为什么 EDSFF 是 PCIe 6.0 时代的必然选择。

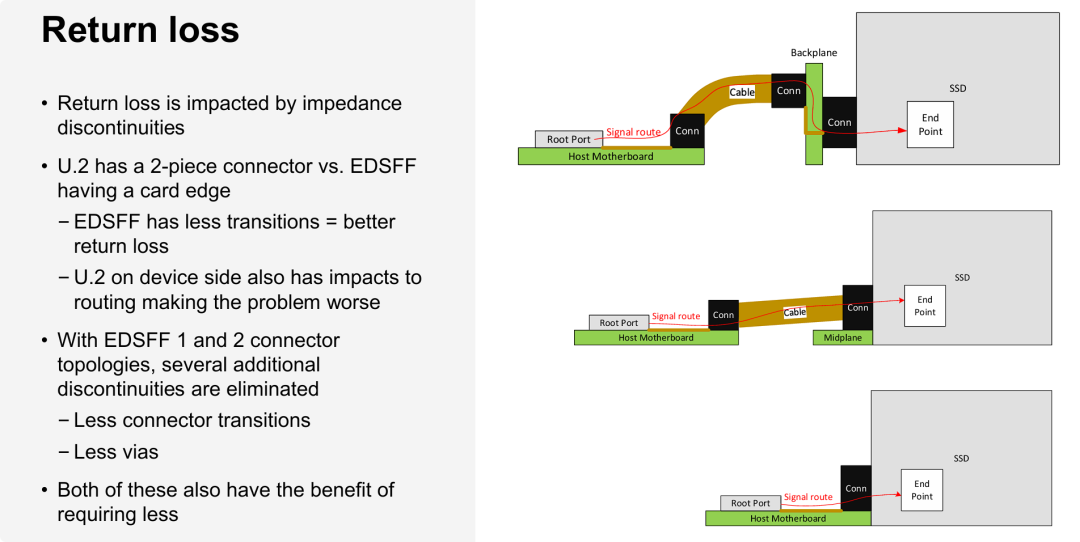

图片揭示了为什么 U.2 在迈向 PCIe 6.0 时力不从心,而 EDSFF 具备优势的深层物理原因:

- 阻抗控制是关键:在 PCIe 6.0 的高频下,信号就像光一样,遇到不平整的界面(阻抗不连续)就会反射回来形成噪声。

- 结构性优势:EDSFF 的金手指设计比 U.2 的传统插槽连接器更简洁,天生反射更小。

- 链路精简:通过 1 连接器直连架构,EDSFF 几乎消除了所有中间“路障”(过孔、线缆转换),这不仅解决了上一张图提到的插入损耗(能量不够) 问题,还解决了本图强调的回波损耗(杂波太多) 问题。

简单来说,EDSFF 不仅让信号“走得远”(损耗小),还让信号“走得稳”(反射小)。

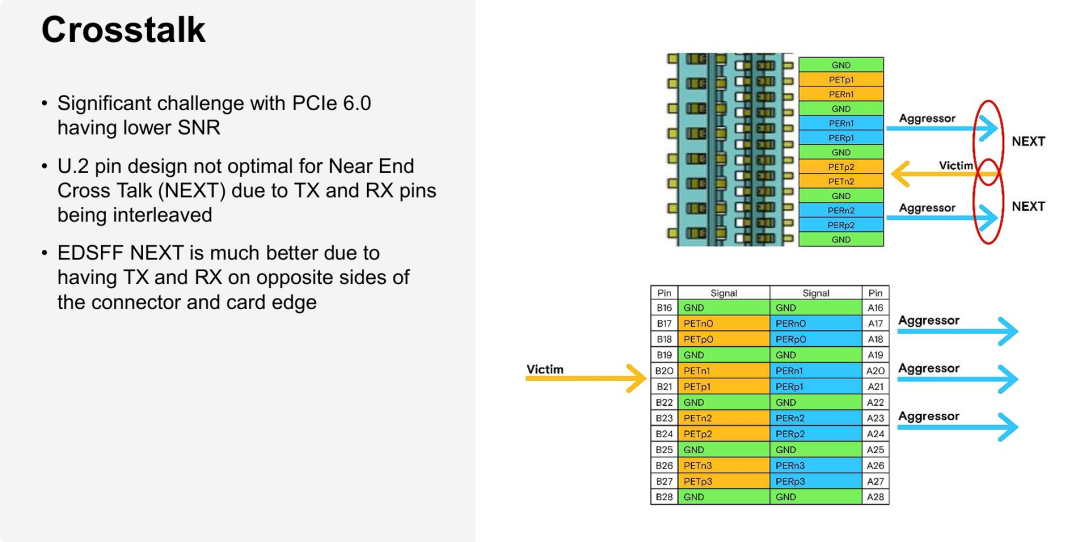

图片揭示了 PCIe 6.0 在 U.2 接口上难以实现稳定传输的又一个物理死穴——电气串扰。

- 引脚隔离是成败关键:在 PCIe 6.0 极高的运行频率下,信号间的相互干扰指数级增加。U.2 接口这种源自 SAS 时代的引脚交错设计,使得发送和接收信号在连接器处几乎是“贴身肉搏”,导致近端串扰严重。

- EDSFF 的“背面隔离”策略:EDSFF 通过将 TX 和 RX 彻底分层(放在 PCB 金手指的正反两面),利用 PCB 基材作为天然的物理屏障,极大提高了信噪比,从而满足了 PCIe 6.0 严苛的信号要求。

如果您正在设计下一代服务器,这张图表其实是在强调:为了维持足够的信号纯净度,物理接口的升级(从 U.2 转向 EDSFF)已经不再是可选项,而是必选项。

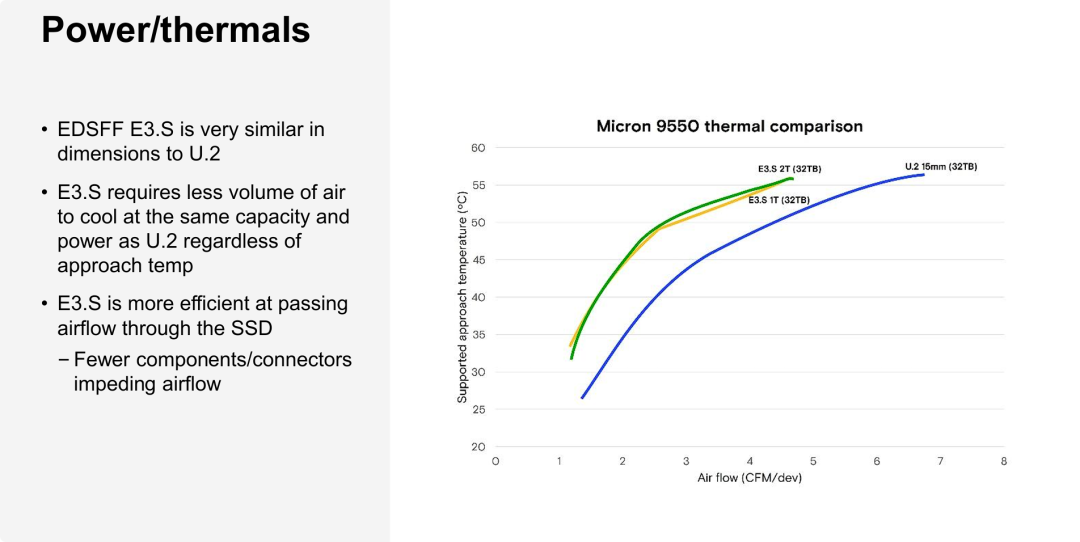

图片展示了 EDSFF(特别是 E3.S)在现代数据中心节能降耗方面的核心竞争力:

- 更高的热效率:E3.S 证明了即便尺寸与 U.2 接近,通过优化内部结构和连接器设计,可以大幅提升散热效率。

- 降低风扇能耗:图表清晰地显示,要达到同样的冷却效果,E3.S 对系统风量的需求远低于 U.2。这意味着服务器可以降低风扇转速,从而节省大量系统层面的功耗。

- 支持更高的环境温度:在风量受限的情况下,E3.S 能够支撑更高的环境温度,这对于提高数据中心运行效率(PUE)至关重要。

总结

比较维度 | U.2 (传统接口) | EDSFF (E3.S/新型接口) | PCIe 6.0 时代影响 |

|---|---|---|---|

行业地位 | 15 年来的主流硬盘规格 | 约 7 年前推出的新一代标准 | EDSFF 是 PCIe 6.0 的必然选择 |

连接器结构 | 两件式连接器 (2-piece) | 金手指卡缘设计 (Card edge) | EDSFF 转换环节少,回波损耗更低 |

信号引脚布局 | TX/RX 引脚交错排列 | TX/RX 分置于 PCB 正反两面 | EDSFF 显著改善了近端串扰 (NEXT) |

PCIe 6.0 规范 | 缺乏设备级官方规范 (No Spec) | 具有明确的设备级损耗规范 | U.2 在超高速传输下的稳定性无法保证 |

拓扑灵活性 | 主要是复杂的 3 连接器拓扑 | 支持 1、2、3 连接器多种拓扑 | 1 连接器拓扑可回收 6dB+ 损耗预算 |

散热效率 | 组件多,严重阻碍气流 | 组件少,气流通过率高 | E3.S 显著降低风扇能耗和冷却风量 |

延伸思考

这次分享的内容就到这里了,或许以下几个问题,能够启发你更多的思考,欢迎留言,说说你的想法~

- 除了技术上的优越性,EDSFF要在数据中心全面取代U.2,还可能面临哪些来自生态系统(如供应链成熟度、服务器模具兼容性、运维人员习惯)的挑战?

- PCIe 6.0的信号完整性设计已如此严峻,您认为当前EDSFF的设计是否为更高速的PCIe 7.0预留了足够的设计裕量?未来是否会出现更彻底的变革,例如在服务器内部小范围转向光互连?

- 在短期内,采用EDSFF替代U.2的服务器设计,其初始物料清单(BOM)成本是否会显著增加?企业应如何权衡这种前期投入与它带来的长期运营成本(TCO)节省?

原文标题:How EDSFF exceeds for PCIe 5.0 and 6.0[1]

Notice:Human's prompt, Datasets by Gemini-3-Pro

#FMS25 #EDSFF接口

---【本文完】---

丰子恺-护生画集-蝴蝶来仪(借有凤来仪)

👇阅读原文,搜索🔍更多历史文章。

- https://files.futurememorystorage.com/proceedings/2025/20250807_SSDT-303-1_Constantine.pdf ↩

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2026-02-15,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录