瑞盟ADC新品MS53115( 参数和噪音评估)

在美丽的杭州,其实也有一家默默努力的信号链公司:

正好三个月在西湖边溜达来着,放个西湖,hhhh

正好上个月在西湖边溜达来着,放个西湖,hhhh

话说回来是:

瑞盟

瑞盟

他们的很多料都很意思,比如之前测速度的就有替代(有空可以测一下),还有一颗小 OP:

这个之后介绍

这个之后介绍

新品MS53115:单电源八通道Σ-Δ型模数转换器,24位分辨率,125 kSPS采样率,±10V输入范围

就是一个很适合工业测量的料,只是一眼看过去,采样率被这么多通道分了就很慢了。

看看芯片de样子

因为这边客户端的评估板还没有搞完,我就先拿 chip 了

因为这边客户端的评估板还没有搞完,我就先拿 chip 了

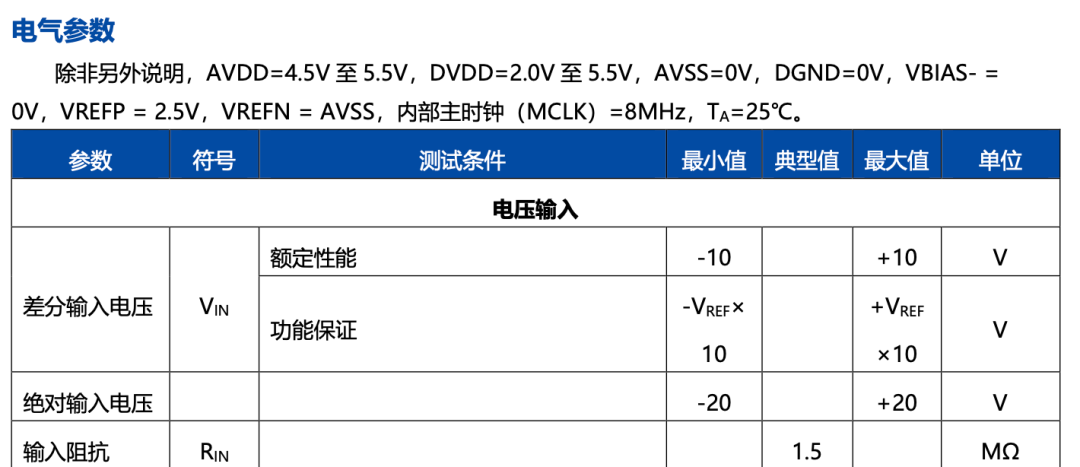

具体参数

因为电气和编程是分开的,我这边编程就先不写了

类型:集成模拟前端的 24 位 Σ-Δ ADC

输入能力:

标称量程:±10 V

允许极限输入:±20 V(内部有分压网络)

输入阻抗:约 1.5 MΩ

通道数:

8 路差分或 16 路单端

最高速:单通道最高 125 kSPS 输出多通道扫描时,每通道最高约 24.845 kSPS(40.25 μs 建立时间)。

一颗自带 ±10V 前端、内部参考、电源 LDO、数字滤波和多通道扫描逻辑的“PLC / DCS 模块专用 ADC 。

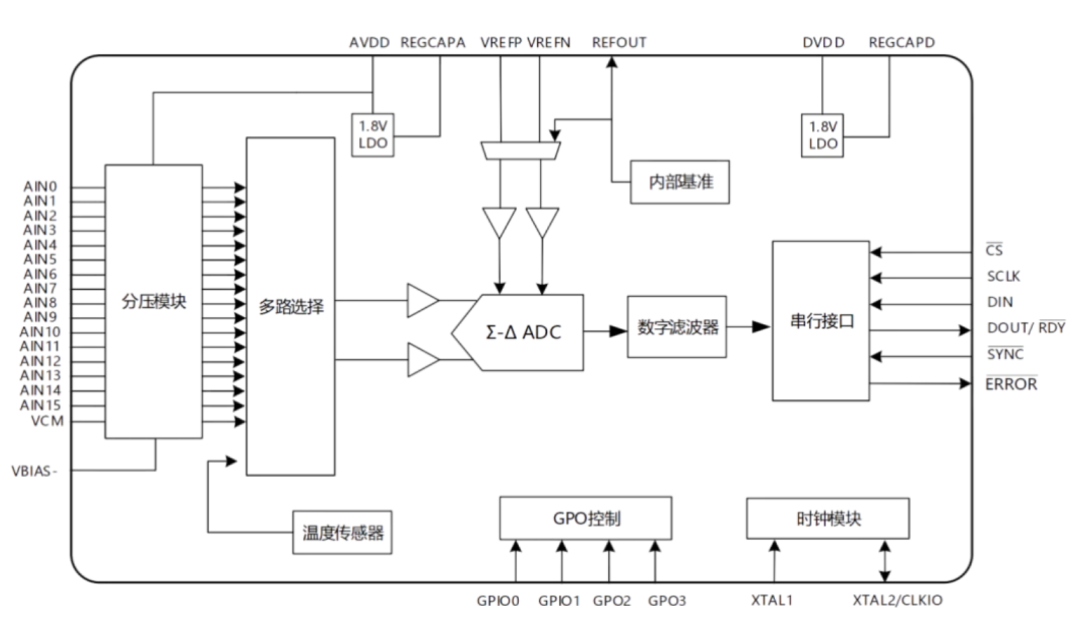

内部框图怎么理解

image-20251201141828632

左侧:16 路 AIN0~AIN15 → 连接到 分压模块 + 多路选择器

分压模块负责把 ±10V(甚至 ±20V 极限)降到内部 ADC 合适的量程;VCM & VBIAS- 用于定义输入的共模/偏置点。

中间:Σ-Δ ADC + 数字滤波器

前面是过采样、调制(Σ-Δ 调制器),后面是可配置的数字滤波(sinc5+sinc1 / sinc3 / 增强型 50/60 Hz 抑制滤波器)。

上侧:内部 2.5 V 参考源 + REFOUT 管脚,可直接外接 0.1 µF 去耦当系统基准。

右侧:串行接口 + GPIO/GPO

标准 SPI 兼容(SCLK / DIN / DOUT / CS),DOUT 复用 RDY;还有 GPIO0、GPIO1、GPO2、GPO3 可做通用控制/状态输出。

下侧:模拟 LDO(REGCAPA)、数字 LDO(REGCAPD)、时钟模块(内部 8 MHz + 外部晶振/时钟)。

简化理解:

“16 路高压输入 → 内部分压 → 可编程 Σ-Δ ADC + 数字滤波 → SPI 输出”,外围只要供电、电容、少量参考/时钟器件,就能直接用。

管脚与供电/参考的关键点

供电与地

模拟电源:AVDD 4.5–5.5 V,相对 AVSS

数字电源:DVDD 2–5.5 V,相对 DGND,且 DVDD 与 AVDD 电平独立

模拟“负电源”:AVSS 相对 DGND 可在 -2.75~0 V(这意味着可以让模拟前端工作在稍微低于数字地的电平,以更好适配 ±10V 输入的内部偏置。)

工业场景通常DGND = 0、AVSS 也接 0(单电源 0–5 V),芯片内部通过分压和偏置处理 ±10V 信号;外面只要保证输入绝对值不超过 ±20V。

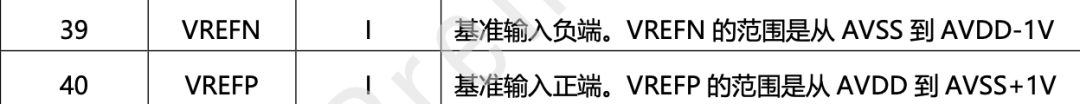

参考电压与 VCM/VBIAS

内部参考:REFOUT = 2.5 V(相对 AVSS),初始精度 ±0.12%(25℃),温漂 ±22 ppm/℃。

外部参考:VREFP / VREFN 差分输入范围:1 V ~ AVDD;可以禁用/启用内部 buffer,限制略有不同(见表 8,“外部基准输入”一段)。

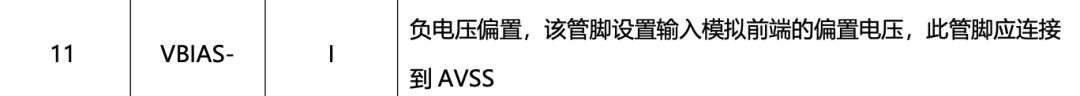

VBIAS-(脚 11):

“负电压偏置”,用来设定模拟前端的偏置电平,应连接到 AVSS;内部的分压模块就是以 VBIAS-/VCM 这些点作为基准做偏移的。

简单说:

VREFP/N 控制“量程标尺”,VCM/VBIAS- 决定“刻度零点在哪”。一般照手册:VCM、AVSS、VBIAS- 都接在模拟地系,内部分压已帮大家处理 ±10V。

模拟输入 AINx

每个 AINx 支持两种配置:

单端模式,AINx 相对于 VCM 测量(相当于 AINx – VCM)。

差分模式;(AIN0, AIN1)、(AIN2, AIN3)…(AIN14, AIN15) 组成 8 组差分对。

重要参数:

标称差分范围:±10 V(满量程)

绝对输入范围:-20 ~ +20 V(相对 AVSS)

输入阻抗:约 1.5 MΩ

说明可以直接把 ±10V 工程量(变送器、电压信号)接上,芯片内部会自动降压到 ADC 工作区间。外面一般只需要简单 RC 滤波+浪涌/过压保护。(后面有一节写这个)

时钟与接口

时钟

内部时钟:8 MHz,精度 ±2.5%

外部晶振:14~16.384 MHz(XTAL1/XTAL2,典型 16 MHz)

外部时钟:8~8.192 MHz(CLKIO)

数字滤波器的输出数据速率 ODR 会根据 主时钟频率 + 内部设置 计算出;手册给了直接的 ODR 表,不用自己推算。

噪声 & 有效分辨率怎么读?

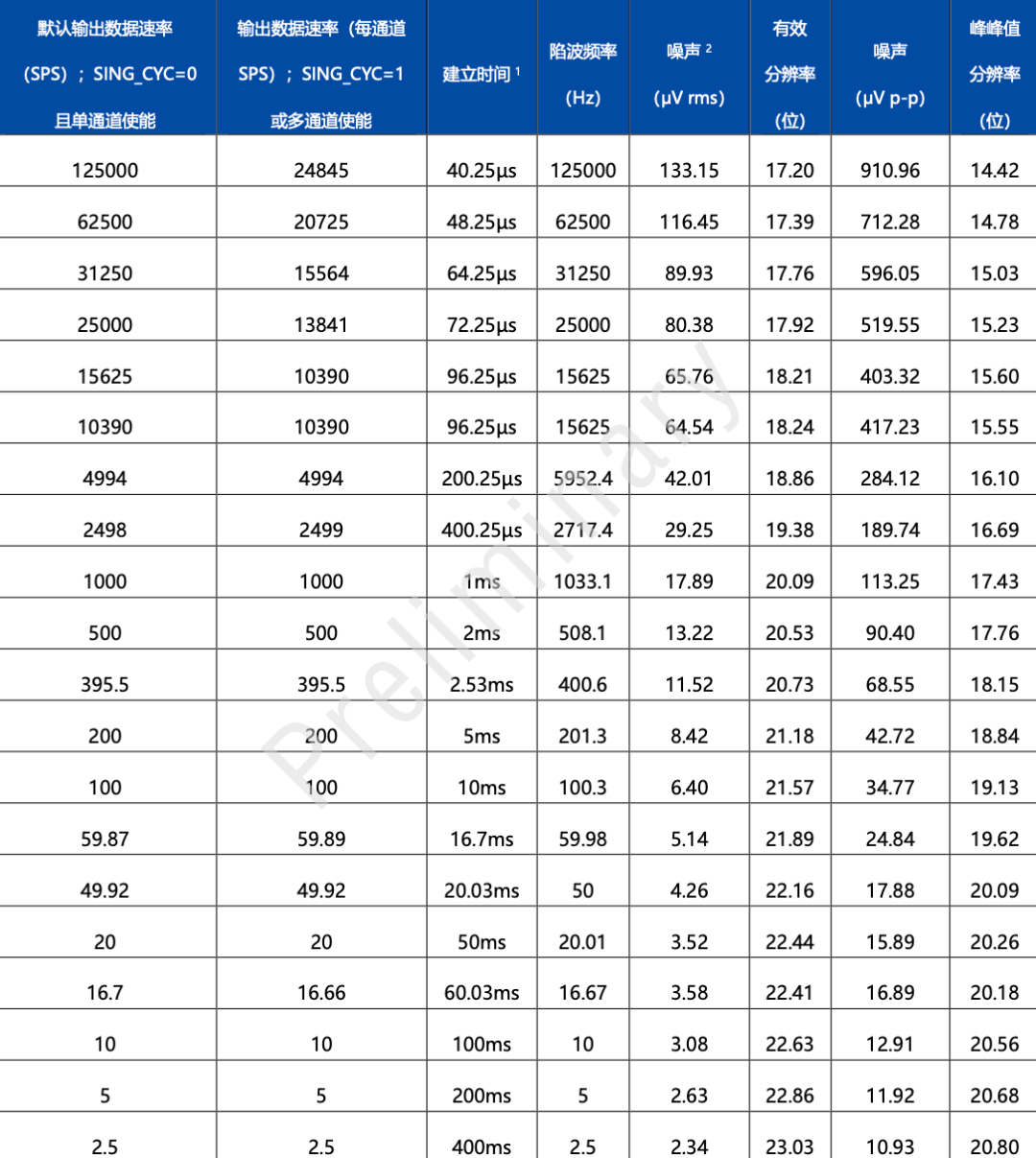

重点看表 1(sinc5+sinc1)与表 2(sinc3)

重点看表 1(sinc5+sinc1)与表 2(sinc3)

每一行里几个关键列:

默认输出数据速率(SPS):芯片整体 ODR(单通道、SING_CYC=0 时)。

输出数据速率(每通道 SPS):多通道扫描 / 单周期模式时,每个通道实际能拿到的 SPS。

建立时间:给某个通道切换过去后,滤波器需要多长时间,输出才完全“稳定在新通道”的数据,通道扫描时的“通道扫描周期 = 建立时间”。

陷波频率:数字滤波器的零点位置,比如 50/60 Hz 陷波(抗工频干扰)。

噪声(µV rms) & 有效分辨率(位):基于 ±10 V 量程算出来的“等效 ENOB”。

噪声(µV p-p) & 峰峰值分辨率(位):用峰峰值噪声对应无失码位数。

典型数值感受一下(sinc5+sinc1,±10V):

125 kSPS(单通道):噪声 ≈ 133 µV rms,ENOB ≈ 17.2 bit,峰峰 ≈ 14.4 bit

2.5 SPS::噪声 ≈ 2.34 µV rms,ENOB ≈ 23.0 bit,峰峰 ≈ 20.8 bit

也就是说:

速度越高 → 有效位数降到 17~18 bit;速度越低 → 可逼近 23 bit 有效分辨率。

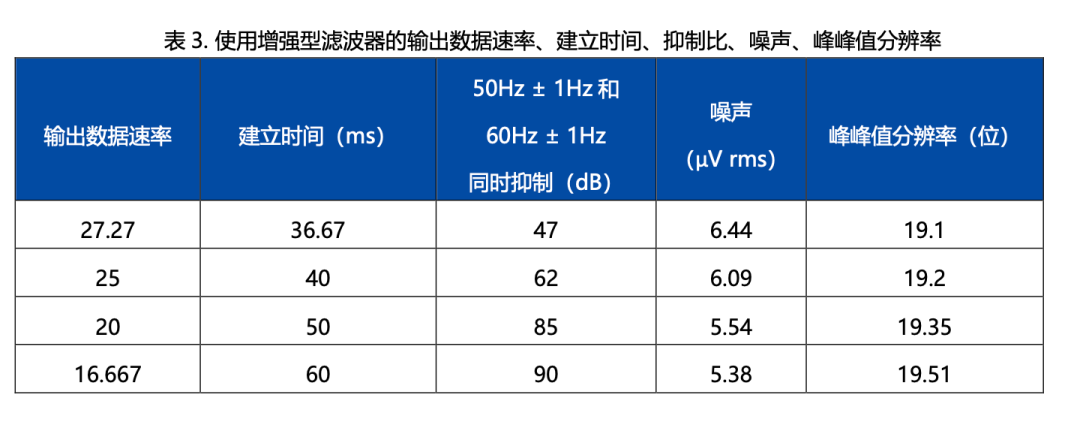

为 50 Hz ±1 Hz 和 60 Hz ±1 Hz 提供额外的抑制;比如 20 SPS 时(建立时间 50 ms):50/60 Hz 同时抑制可达 85 dB,噪声只要 5.54 µV rms,峰峰分辨率 ≈ 19.35 bit。(这就是 “电能计量/工控” 典型场景:慢速 + 超强 50/60 Hz 抑制。)

评估噪音

这颗 53115 的“测量极限”本质上是:±10 V 量程下,单通道慢速 sinc3 模式时,噪声大约 2.5 µV_rms、约 11 µV_p-p,对应噪声无失码分辨率 ~20.8 bit,等效有效分辨率 ~22.9 bit;高速多通道模式(sinc5+sinc1,125 kSPS)时,噪声要大得多,约 133 µV_rms,对应 ~17.2 bit 有效分辨率、14.4 bit 无失码分辨率。

量程方面:额定性能保证在 ±10 V,输入阻抗约 1.5 MΩ;绝对允许输入 -20 V~+20 V,但这段只是“安全不坏”,不是保证精度的测量范围。

具体评估:噪音情况& 能测到多小 / 多大

先定标尺:LSB 和理论极限

芯片标称是 24 bit Σ-Δ,额定差分输入范围 ±10 V(FSR = 20 V)。

1 LSB(理论量化步进)

理想 24 bit ADC 的量化噪声_rms:

实际 datasheet 里给出的噪声要明显大于 0.34 µV_rms,所以系统噪声是由前端+调制器+参考等决定的,远大于纯量化噪声,24 bit 更像是“码宽”,而不是噪声自由分辨率。

不同模式下的噪声情况

sinc5 + sinc1(多通道/高速)

表 1 是使用 sinc5+sinc1 滤波器、±10 V 输入时,在不同 ODR 下的噪声与分辨率:

挑几个关键点(典型值,外部 Vref、0 V 输入):

每通道 ODR | 噪声 (µV_rms) | 有效分辨率 (bit) | 噪声 (µV_p-p) | 无失码分辨率 (bit) |

|---|---|---|---|---|

125 kSPS | 133.15 | 17.20 | 910.96 | 14.42 |

5 kSPS | 42.01 | 18.86 | 284.12 | 16.10 |

1 kSPS | 20.09 | 17.89 | 113.25 | 17.43 |

100 SPS | 6.40 | 21.57 | 34.77 | 19.13 |

20 SPS | 3.52 | 22.44 | 15.89 | 20.26 |

2.5 SPS | 2.34 | 23.03 | 10.93 | 20.80 |

高速 125 kSPS 时

噪声 ≈ 133 µV_rms,相当于 112 LSB_rms 左右;只看“无失码分辨率”只有 ~14.4 bit,更像是一个±10 V、14~15 bit 无失码的多通道高速 ADC。

把速率降下来(例如 5 kSPS)

噪声压到 42 µV_rms,噪声自由分辨率能到 ~16 bit 多,再往下(≤100 SPS),就能接近 20bit 级的无失码分辨率。在多通道扫场景下,是用 ODR 换噪声——速率越低,噪声越小,真正能用的有效 bits 越高。

sinc3(单通道/低速高精度)

表 2 是 sinc3 滤波器,主要针对单通道或“少通道、低速”的高精度应用。

同样挑几个:

每通道 ODR | 噪声 (µV_rms) | 有效分辨率 (bit) | 噪声 (µV_p-p) | 无失码分辨率 (bit) |

|---|---|---|---|---|

5 kSPS | 29.89 | 19.35 | 200.67 | 16.60 |

1 kSPS | 13.62 | 20.49 | 91.39 | 17.74 |

100 SPS | 4.73 | 22.01 | 22.85 | 19.74 |

20 SPS | 3.19 | 22.58 | 14.90 | 20.36 |

2.5 SPS | 2.52 | 22.92 | 10.93 | 20.80 |

同样的 ODR 下,sinc3 的噪声总是比 sinc5+sinc1 更低一点,尤其在低速时更明显;在 2.5 SPS 时,噪声 2.52 µV_rms,对应有效分辨率 22.92 bit、无失码 20.8 bit,已经非常接近 datasheet 能给出的“极限”。

应用说明里也明确说:sinc3 是为了单通道、低速时获得最优噪声特性,建立时间关系式 t_settle = 3/ODR。

增强型 50/60 Hz 抑制滤波器(工频环境)

表 3 是“增强型 50Hz+60Hz 抑制滤波器”,主要是牺牲一点噪声来换双工频高抑制:

ODR (SPS) | 建立时间 (ms) | 50/60 Hz 抑制 (dB) | 噪声 (µV_rms) | 无失码分辨率 (bit) |

|---|---|---|---|---|

27.27 | 36.67 | 47 / 64 | 6.44 | 19.1 |

25 | 40 | 62 / 69 | 6.09 | 19.2 |

20 | 50 | 85 / 85 | 5.54 | 19.35 |

16.667 | 60 | 90 / 90 | 5.38 | 19.51 |

可以理解为:如果现场工频干扰很重,想要 50 Hz 和 60 Hz 同时深度陷波,就用这个增强滤波模式,代价是噪声略大一点、分辨率退到 19~19.5 bit 左右。

噪声决定的“最小可测分辨率”

这里可以分三层来理解:

单次读数分辨率(不做平均)

以最优模式(sinc3、2.5 SPS)为例:噪声 ≈ 2.5 µV_rms,对应无失码分辨率 ~20.8 bit → 等效 “干净 code 步进” ~ 11 µV_p-p;也就是说:如果你只看原始输出,不做平均、不过滤,能比较稳定区分的最小变化量,大约就是 10 µV 级别。

高速模式(125 kSPS,sinc5+sinc1)时:噪声 ≈ 133 µV_rms,不做平均时你能分得开的最小变化量其实是 上百 µV,更像 14~15 bit 的无失码。

通过平均/数字滤波压噪声

因为表 1/2 中的噪声是在固定 ODR 下、简单算统计量得到的,如果你还在 MCU/上位机里再做平均:噪声理论上会按 下降(前提是噪声近似白噪声、没有强 1/f 和漂移);例如在 2.5 SPS 模式下,再平均 100 个样本(约 40 s 的时间),等效噪声可以压到 ~0.25 µV_rms 量级;这个时候量化噪声 (~0.34 µV_rms) 就开始浮出水面,再往下压就难了。

但是,现实中我们还会遇到:参考源的 0.1–10 Hz 噪声(内部 REFOUT 本身 0.1–10 Hz 噪声 ≈ 9.2 µV_rms,对 2.5 V 参考来说);前端电阻的热噪声、传感器本身噪声;温度漂移引入的缓慢漂移(平均不掉);所以实际极限 DC 分辨率通常会被这些慢变化噪声和漂移卡住,在一个合理时间窗口内(比如几十秒)很难做得比 1 µV 级好太多。

有效分辨率 vs 无失码分辨率

datasheet 里给了两个分辨率概念:

有效分辨率:用 rms 噪声换算出来,相当于 SNR 对应的 ENOB。

峰峰值分辨率(无失码):用 p-p 噪声算出来,等价于“码字不会跳字”的 bits 数。

从“测量极限”的角度看:如果关心“能看到多小的变化”(比如做 FFT、统计分析),看有效分辨率;如果关心“显示的数字要稳定、不抖码”(比如数字表读数),看峰峰值/无失码分辨率。

在合理平均时间内,做到 10 µV 级无失码分辨率、几 µV_rms 的分辨能力是比较现实的目标;高速多通道时要接受分辨率退到 15~18 bit 这一档。

综合评估测量的带宽范围

我之前的文章也写了,这个多通道的切换是均分采样率以及也是需要稳定时间的,那不可避免的也是需要评估一下。

先统一一下概念:三个“带宽”

对 53115 来说,跟设计相关的带宽其实有三层:

数字输出数据速率 ODR

单通道:2.5 SPS ~ 125 kSPS;对应“数学上的”奈奎斯特带宽 = ODR/2。

内部数字滤波器的有效通带

sinc5+sinc1 / sinc3 是标准 sinc 滤波器,在整数倍 ODR 处有“陷波”,频响从 DC 开始平坦,接近 ODR 时已经明显衰减,然后在 “陷波频率”处为 0。表 1/2 里的“陷波频率”基本都等于当前 ODR;增强型 50/60 Hz 滤波器是在 sinc5+sinc1 后面再叠一层后置滤波,专门把 50 Hz ±1 Hz,60 Hz ±1 Hz 打成深陷波。

多通道扫描时,每路的“等效带宽”

表 1/2 可以看到多通道 / 单周期模式时,每通道的 ODR 会降低,同时建立时间 = 1 / 通道转换速率;也就是:想多通道、单周期稳定,就要用更低的 per-channel ODR,对应每路带宽也会降。

在工程上,通常会保守一点,用规则:

能保证幅度响应还比较平坦的“测量带宽” ≈ 0.2~0.3 × ODR(再往上虽然没到陷波,但幅度/相位已经明显劣化)

各种滤波模式的“可用带宽”大致怎么估

sinc5 + sinc1(多路复用/高速模式)

应用说明里明确说:

sinc5+sinc1 适合多路复用场景,在不超过 10 kSPS 的采样率下可以做到单周期建立;sinc5 模块固定 125 kSPS,sinc1 模块通过抽取控制最终 ODR。

结合 datasheet 表 1:单通道时 ODR 最大 125 kSPS,对应陷波频率也是 125 kHz。

通常可以这么估:

单通道 125 kSPS,目标是“能看到波形就行”:理论奈奎斯特,62.5 kHz;sinc5+sinc1 通带平坦区实际大约在 0~20 kHz 左右是比较靠谱的;20~40 kHz 带着明显衰减还能看;接近 62.5 kHz 前就已经很塌了。

要兼顾多通道、带宽和单周期稳定

手册说“单周期建立只在 ODR≤10 kSPS 时对 sinc5+sinc1 有效”。

举例:设置 per-channel ODR = 5 kSPS:

奈奎斯特 = 2.5 kHz(实际建议把有效测量带宽控制在 1~1.5 kHz 左右,这样相位/幅度都还比较好。)

总结:sinc5+sinc1 模式下“可用测量带宽”大致是 0~(0.2~0.3)×ODR,每通道 ODR 又受多通道和单周期约束。

sinc3(单通道/高精度)

应用说明里给了两个关键式子:

建立时间:

数据速率与滤波抽取比关系:

这是典型的 sinc³ 滤波器,频响性质:通带更“收敛”:高频滚降更陡 → 低速下噪声性能最好(datasheet 表 2 的 ENOB 就是基于这个);但同样,在接近 ODR/2 的区域,幅频响应已经显著衰减。

工程上可以用一个经验值:

对 sinc3 来说,比较平坦的带宽大致在 0~0.25×ODR 左右;再往上(接近 0.5×ODR)会有明显 droop。

例如用 sinc3,ODR = 1 kSPS(表 2:噪声 ~13.6 µV_rms)。

奈奎斯特 = 500 Hz

建议的“高保真测量带宽” ≈ 0~200~250 Hz。

ODR = 100 SPS:奈奎斯特 = 50 Hz;实际适合测 0~20 Hz 左右的慢变化(位移、温度、力、工频 RMS 等)。

所以:sinc3 更适合“低频高分辨率场景”,典型就是几十赫兹以内的信号。

增强型 50/60 Hz 滤波器(能量计量/强工频干扰)

增强型滤波器是对 sinc5+sinc1 的后置滤波,最高 ODR ≈ 27.27 SPS。

表 3 里给的几个典型点:

ODR (SPS) | 建立时间 (ms) | 50/60 Hz 抑制 (dB) | 噪声 (µV_rms) |

|---|---|---|---|

27.27 | 36.7 | 47 | 6.44 |

25 | 40 | 62 | 6.09 |

20 | 50 | 85 | 5.54 |

16.667 | 60 | 90 | 5.38 |

这类滤波器目标很明确:频率在 50 Hz±1 Hz、60 Hz±1 Hz 范围内的干扰被强烈抑制(最多 90 dB);换来的代价是 ODR 很低,通带很窄。

如果用 ODR = 20 SPS(奈奎斯特 10 Hz):实际适合的测量带宽就是 0~8~9 Hz 那一档。

多通道扫时,每路带宽还能剩多少?

看 datasheet 的表 1/2,会发现两类数据:

“默认输出数据速率(SING_CYC=0,单通道使能)”;“输出数据速率(每通道,SING_CYC=1 或多通道使能)”。

规律是多通道时,每个通道的 ODR = 总 ODR / 有效通道数(再加上一些内部 pipeline 影响);建立时间 = 1 / 通道转换速率;于是 每路 Nyquist 变小,可用带宽也随之减小。

通过噪音给的工作区间

把前几轮噪声讨论加进来,可以粗略给出 53115 的三个典型“工作区间”:

高速多通道区(sinc5+sinc1,ODR ~ 10–125 kSPS)

单通道:最大 ODR=125 kSPS,可用带宽最多做到 10~20 kHz 级别。

多通道时:每路 ODR 下降,按 0.2~0.3×ODR 估带宽。

噪声在几十~百余 µV_rms 量级,对应 17~19 bit 有效分辨率。

中速高精度区(sinc3,ODR ~ 100–5 kSPS)

单通道/少通道应用,带宽 10 Hz~几百 Hz;噪声可压到 10 µV_rms 以内,对应 20~22 bit 有效分辨率。

低速超高分辨率 & 强工频抑制区(sinc3 or 增强滤波,ODR ≤ 20–25 SPS)

带宽 0~几 Hz,适合慢变化量/ RMS 量;sinc3 2.5 SPS 时噪声 ~2.5 µV_rms,对应 22.9 bit 有效分辨率、20.8 bit 无失码;增强滤波器 20 SPS 时,对 50/60 Hz±1 Hz 干扰抑制 ~85 dB,噪声 ~5.5 µV_rms。

简单总结一句话

理论上:53115 单通道最高 125 kSPS,奈奎斯特 62.5 kHz,但考虑 sinc 滤波器的幅度滚降,“高保真可用带宽”通常取 0~(0.2~0.3)×ODR。(多通道时每路 ODR = 总 ODR / 通道数,再按照上面比例估带宽。)

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-12-01,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录