回答读者问题:高速 ADC 中的 1/f.补篇

回答读者问题:高速 ADC 中的 1/f昨天后半夜发的是上篇,下午起来发第二篇。

一看 Tony 就在出差,干河南去了

一看 Tony 就在出差,干河南去了

Tony 老师先肯定了这个结论

还有咱们的 pg(屁股?)hhh,开个玩笑

还有咱们的 pg 老师(屁股?)hhh,开个玩笑

本来是没有想的这么详细的,不过既然提出那就尝试一下这个结论。

关于真实的案例

这是问题所在

这是问题所在

1 GS/s、N=16384(T=16.384 µs,Δf≈61 kHz)这类高速短记录里,1/f 噪声对 SNR 基本可以忽略。原因是窗口太短,所有“远低于 1/T 的 1/f 成分”在这段时间内只表现为近似常值或非常缓慢的斜率,不会像白噪声那样在信号带内均匀铺开。

为什么“只观察到一小段”也几乎不影响 SNR?

把 1/f 噪声建模为 。

在有限窗口内,真正能“进带”的频率下限不是 0,而是 。对单个 FFT bin 或窄带测量,噪声积分近似是:

其中 (矩形窗)或 (Hann 窗)。

代回 :(或 ),而且 K 本身很小(通常在 1/f 转折频率 处满足 ,即 )。

对高速前端,常见 远低于 ,于是:

参数 :

若 (约 -36 dB);

若 (约 -58 dB);还没算窗泄漏、均值/趋势去除的进一步抑制;实测影响应该通常更小。

对这么短的记录时间, 的 1/f 成分在时域看起来就像“一个常数 + 一点点斜坡”。

常数项被去均值抹掉,斜坡被去趋势吃掉;即使不预处理,它对高频正弦的 FFT主瓣几乎没有能量耦合(近似正交),只在极低频附近引起轻微泄漏。

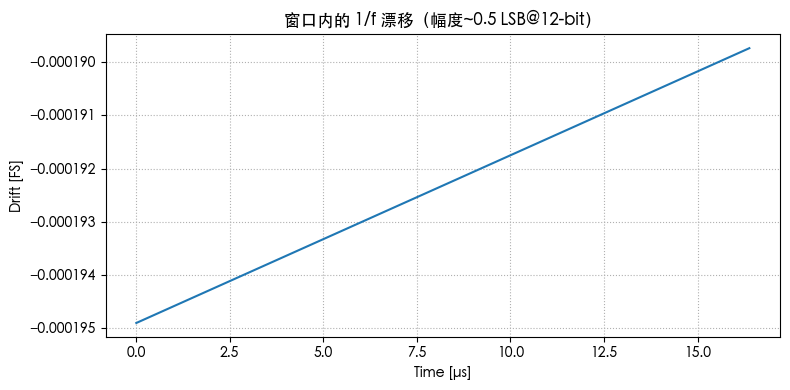

仿真一下

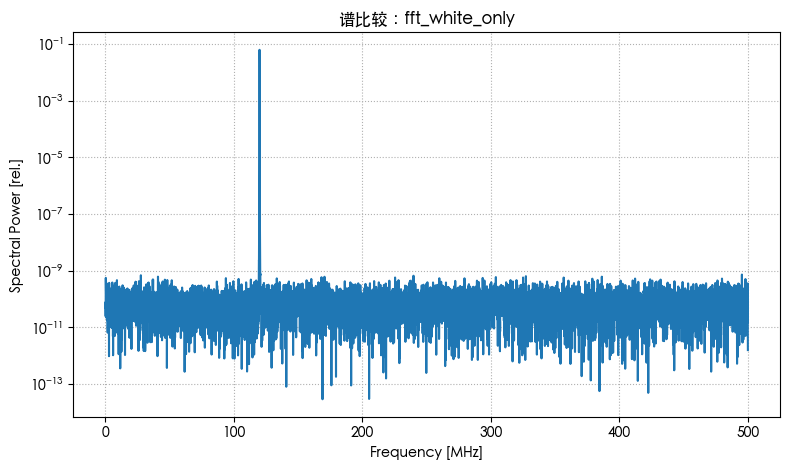

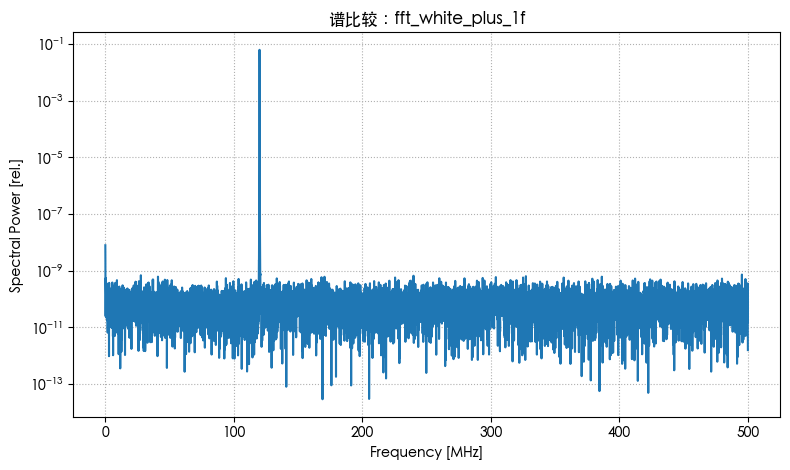

用 Python 复现:1 GS/s、N=16384、fin=120 MHz,叠加白噪声(σ=2 mFS)和一个0.5 LSB@12-bit 等级的超低频 1/f 漂移(窗口内几乎不变化);基于 FFT 的 SNR 结果:

白噪声仅:35.68 dB

白噪声 + 1/f(未处理):35.68 dB

+去均值:35.68 dB

+去线性趋势:35.68 dB

也就是说,在这类高速短记录下,加入可观(相对量级不小)的 1/f 漂移,SNR 基本不变。窗口内的 1/f 看起来就是一个几乎恒定的偏置(配图里那条几乎平的线),不会显著进入信号带噪声功率。

窗口内 1/f 漂移(0.5 LSB)

窗口内 1/f 漂移(0.5 LSB)

FFT:白噪声

FFT:白噪声

FFT:白噪声 + 1/f

FFT:白噪声 + 1/f

1 GS/s、16384 点:。只要你的 1/f 转折 (现实中通常如此),其贡献对单音 SNR 可忽略。

真正主导高速 ADC SNR 的通常是白噪声与采样抖动(aperture jitter):

在百兆~吉赫输入频率时, 的 ps/fs 级变化比任何 1/f 噪声都更“致命”;如果改成长时间观测(例如做数字抽 decimation,T → 秒级),那时 很低,1/f 才会显形并开始影响基带测量(这就是低速精密 ADC 要非常关心 1/f 的原因)。

关于PG老师的回复

(俺不是IC 设计,纯纯爱好者,如有错误,这算免责声明了);PG 老师说:高速 ADC / CT ΣΔ 里,时钟的 1/f 噪声(特别是 PLL / VCO 的 1/f³ 相噪) 到底要不要管?

基础:1/f 噪声 ≠ 只存在低频信号里

模拟器件(晶体管、电阻)都有“1/f 噪声”;到振荡器(VCO)里,它会被上变频成相位噪声;相位噪声离载波越近,斜率越陡(通常是 1/f³ 或 1/f²);这就是所谓的 “近端相噪”(Close-in phase noise)。

所以:

1/f 在时钟系统中,表现为相位抖动;虽然信号是 GHz 的,但低频相噪会让时钟边沿在时间轴上“抖”,等价于时域里的 jitter(抖动)。

相位噪音

这是一个非常稳定的时钟信号:

理想情况:

/\ /\ /\ /\ /\

/ \ / \ / \ / \ / \

---/----\----/----\----/----\----/----\----/----\----> 时间

每个上升沿都间隔完全一样,这是一个理想的“纯正弦”或完美时钟。

现在,现实中因为晶体管噪声、电源干扰等影响,每个上升沿都会轻微抖动:

实际情况(有相位噪声):

/\ /\ /\ /\ /\

/ \ / \ / \ / \ / \

---/----\----/----\--/----\-----/----\---/----\----> 时间

↑ ↑ ↑ ↑

比理想早 晚一点 再早一点 再晚一点...

这些上升沿时刻不再固定,就是所谓的“相位抖动”;在频谱上,这种“时间抖”表现为主频旁边的噪声裙边。

在频谱仪上看到的样子

一个干净的时钟,在频谱上是这样:

^

|

| (理想时钟)——干净的单线

|

-------|-------------------------------------> 频率

带有相位噪声的时钟:

^

| /‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾\

| / \

|___________/ \_____________> 频率

f0-Δf f0 f0+Δf

中心的尖峰是主频 ,两边“扩散”的裙边就是相位噪声功率谱密度,单位 dBc/Hz。

数学定义

相位噪声 定义为:

主载波两侧带宽内的功率载波功率

单位是 dBc/Hz。

比如:,表示离载波 1 kHz 处的噪声功率比主载波低 100 dB(每 Hz 带宽)。

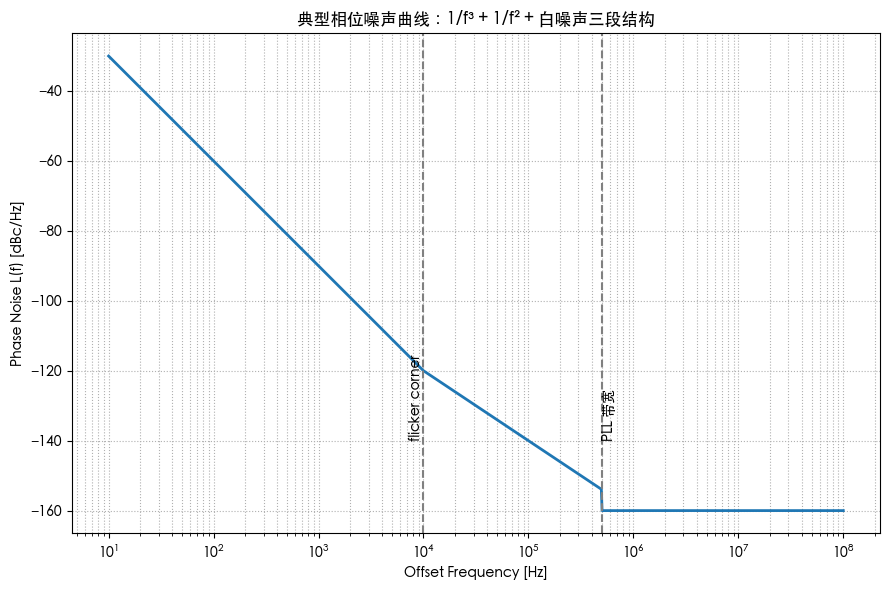

典型相位噪声曲线长这样:

L(f)

|

-40 |\

| \

-60 | \

| \ <- -30 dB/dec 斜率 = 1/f³ 区

-80 | \____

| \

-100| \__ <- -20 dB/dec 斜率 = 1/f² 区

| \

-120| \____ <- 平坦区 = 白噪声

+----------------------------------> 频率偏移 (Hz)

10 100 1k 10k 100k 1M

这样的

这样的

左侧斜率 −30 dB/dec(1/f³):由晶体管 1/f 噪声上变频而来,称为 flicker 区→ 在图中 10 kHz 处标为 flicker corner,拐点前噪声随频率快速上升。

中间斜率 −20 dB/dec(1/f²):对应白频率噪声(VCO 热噪声积分后的形态)。

右侧平坦段:白相位噪声地板,通常由放大器和缓冲白噪声决定→ 在 500 kHz 处标出 PLL 带宽,带宽之后噪声被“钳平”。

这三段对应不同噪声机制:

区域 | 特性 | 物理来源 |

|---|---|---|

1/f³ 近端区 | 低频漂移型相噪 | 晶体管的 flicker(1/f) 噪声上变频 |

1/f² 区 | 白频率噪声 | 热噪声、器件白噪声经积分 |

平坦区 | 白相位噪声 | 高偏移处的随机抖动地板 |

相位噪声就是“时钟在频域里的不稳定性”;在时域,它表现为边沿 jitter;在频域,它表现为载波旁边的噪声裙边。

这点“时间抖动”为什么这么要命?

高速 ADC 或 CTΣΔ 在采样瞬间,假设输入是正弦波:

如果采样时刻漂了一点点 Δt,那么电压就差了:

电压误差跟输入频率成正比,频率越高、抖动越大,SNR 就越糟。

举个例子:

抖动(σₜ) | 在 200 MHz 输入下的理论 SNR 限制 |

|---|---|

30 fs | 88 dB |

50 fs | 84 dB |

100 fs | 78 dB |

200 fs | 72 dB |

500 fs | 64 dB |

即使只是100 fs(1×10⁻¹³ s),对高频采样已经是灾难级别的误差。

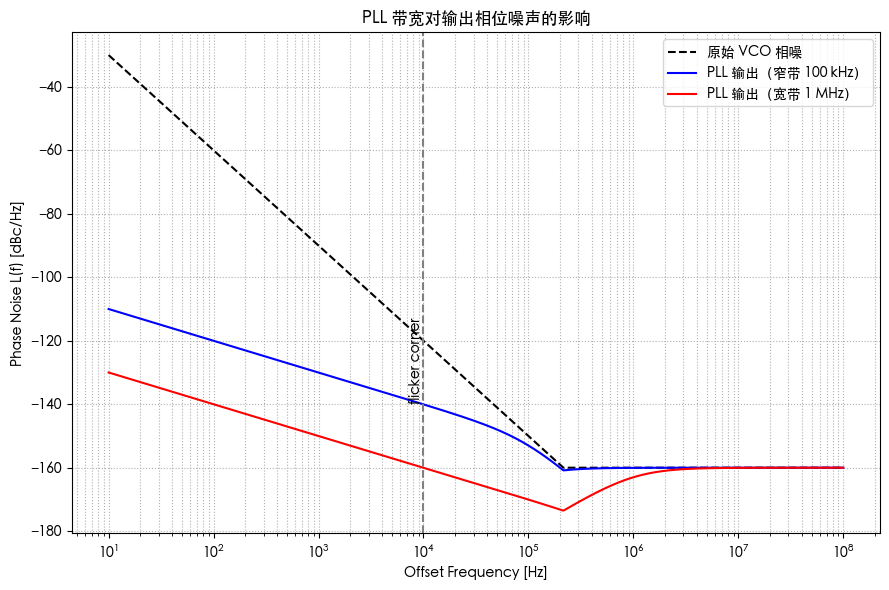

为什么要特别关注 “PLL + VCO”?

因为大多数系统的时钟都来自它,其中VCO 自身的噪声主要是 1/f³(近端)+ 白噪声(远端);最后PLL 的带宽决定了哪些噪声“能过来”;如果 PLL 带宽设太宽→ 把 VCO 的近端 1/f³ 区域也放进输出,造成高抖动;如果太窄:→ 虽然滤掉了 VCO 噪声,但参考端 / 分频器 / 鉴相器的噪声会被放大进来,所以带宽要能压掉参考噪声,但不能太宽把 VCO 1/f³ 放出来。

输出带宽

输出带宽

曲线 | 含义 | 特点 |

|---|---|---|

黑虚线 | 原始 VCO 相噪 | 左边是 −30 dB/dec(1/f³),右边平坦 |

蓝线 | PLL 带宽 = 100 kHz(窄带) | 低频抑制得多,输出更干净,但反应速度慢 |

红线 | PLL 带宽 = 1 MHz(宽带) | 能跟随快变化,但也把近端 1/f³ 噪声放出来 |

Flicker corner 左侧的斜坡是“噪声大本营”,如果 PLL 带宽跨过这个点,就等于把这片“抖动山”放出来。

CT ΣΔ 时钟的 里面的1/f³

连续时间 ΣΔ(CTSDM)是“边沿驱动型系统”:调制器里的积分器、反馈 DAC、比较器全靠时钟边沿;边沿 jitter → 反馈 DAC 的时序误差;这个误差经过 NTF(噪声整形)后,可能被“shape”进信号带里;最后底噪抬高、近载波有“裙边”杂散。

所以当时钟来自 PLL/VCO 时,“低频”不等于“无关”。近端 1/f → 上变成 VCO 的 1/f³ 相噪,再经过 PLL 带宽传递,最后以等效抖动 σₜ的形式限制高速系统(含 CTΣΔ)的 SNR / SFDR;并且在 CTΣΔ 里,反馈 DAC 的时钟边沿抖动还会把噪声形状“混进去”。

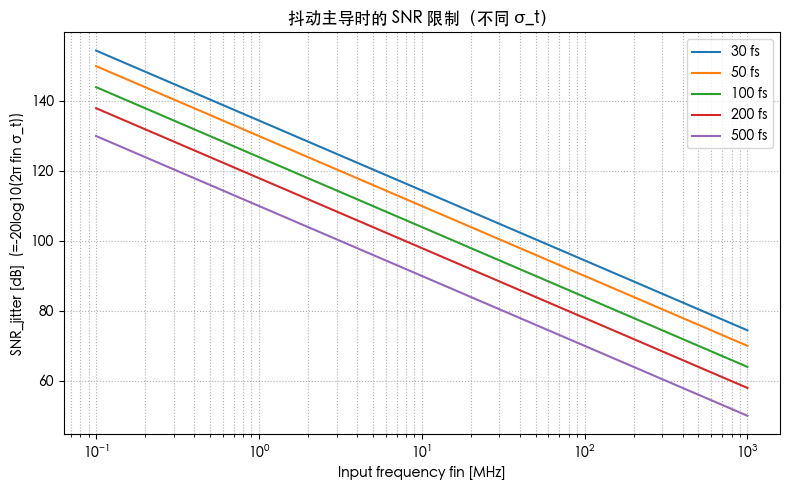

抖动主导的 SNR 上限

我画了多条 σₜ(30/50/100/200/500 fs)的曲线,看看随 提升 SNR 如何快速下滑:

image-20251029144324459

下载:

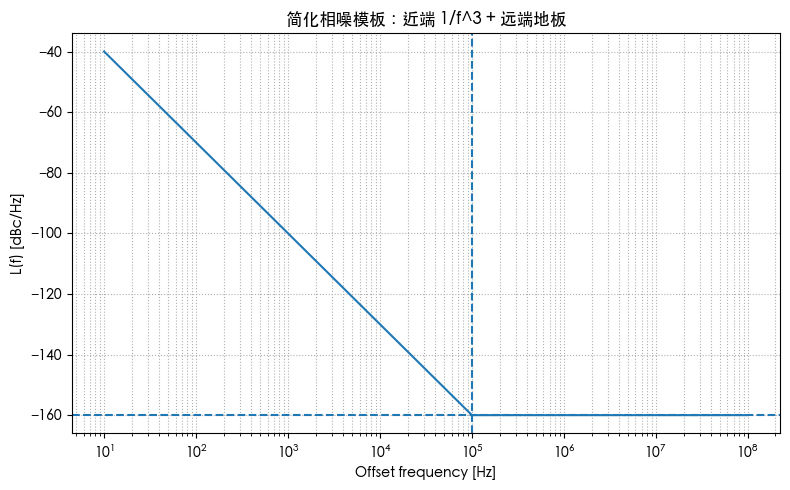

用“近端 1/f³ + 远端白地板”的相噪模板积分得到 σₜ(工程级近似,用于量级判断) 关系(常用近似):

dBc/Hz、白地板 -160 dBc/Hz,近端斜率 dB/dec(1/f³)。

结果(10 Hz..10 kHz vs 10 Hz..1 MHz 两种积分带宽):σₜ 都约 5.0 ps;说明近端 1/f³ 区域占主导,把上限从 10 kHz放到 1 MHz 很难明显改变 σₜ,反而降低 1 kHz–10 kHz 区间的近端噪声才最有效。

image-20251029144623228

决定性的是“近端(1/f³)积分”。如果 VCO 的 flicker corner 高、1 kHz~10 kHz 的相噪差,就算高速,SNR 也会被 σₜ“卡住”;PLL 带宽放得再宽,若近端没压住,提升有限。

采样/量化路径对一般采样系统:抖动以上式限制 SNR,且随 放大。对 CTΣΔ,更要注意量化器时钟与 DAC 反馈脉冲的边沿抖动:反馈 DAC 边沿误差≈输入端等效扰动,大小与被积器输入瞬时斜率相关;该扰动经过 NTF(Noise Transfer Function)被“形状化”,可能把近端 1/f³ 的相噪与量化噪声发生混频/互调,形成近载波裙带或带内底噪抬升。

“VCO 相噪 corner 会变”的原因这是上面提到的重点:AM→PM/PM→PM 的非线性上混频比例受器件偏置和温度(热噪)影响,导致等效 1/f³ corner随工况漂移。换言之,同一 VCO/PLL,在不同电源/温度/KVCO 条件下,近端相噪形貌会变。

后记

其实不复杂,信号处理和图像一样都是一个链条,我们书上是完美的情况,现实不美好就给它加各种误差项,使用信号与系统这套东西传递计算,主要还是频域关心的多。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-10-29,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录