来自荷兰的Tie Pie USB 示波器 HS6 DIFF(最高垂直分辨率到 16bit)

来自荷兰的Tie Pie USB 示波器 HS6 DIFF(最高垂直分辨率到 16bit)

云深无际

发布于 2026-01-07 13:20:30

发布于 2026-01-07 13:20:30

仇老板好玩的真多,今天是他的一个示波器,说实话,这是我用的最舒服的桌面仪器,没有之一,真真正正的硬件强大,软件易用。

测试

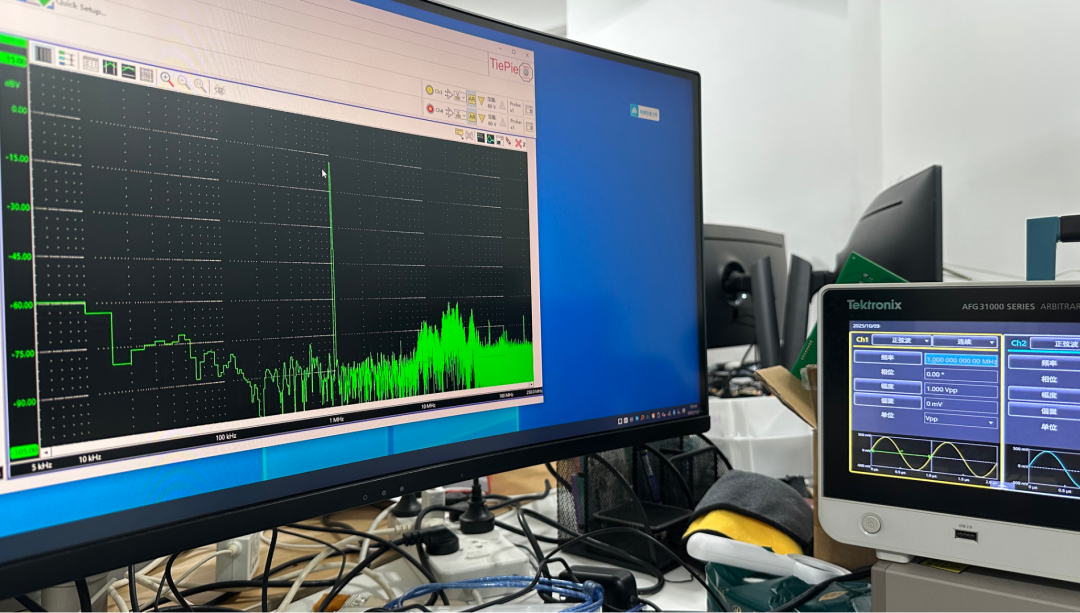

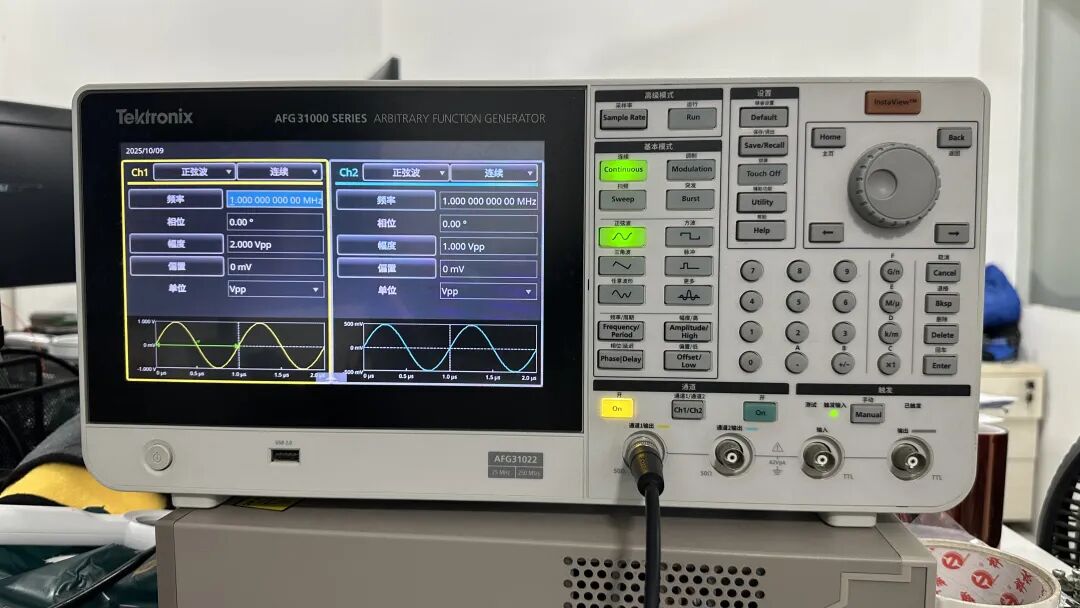

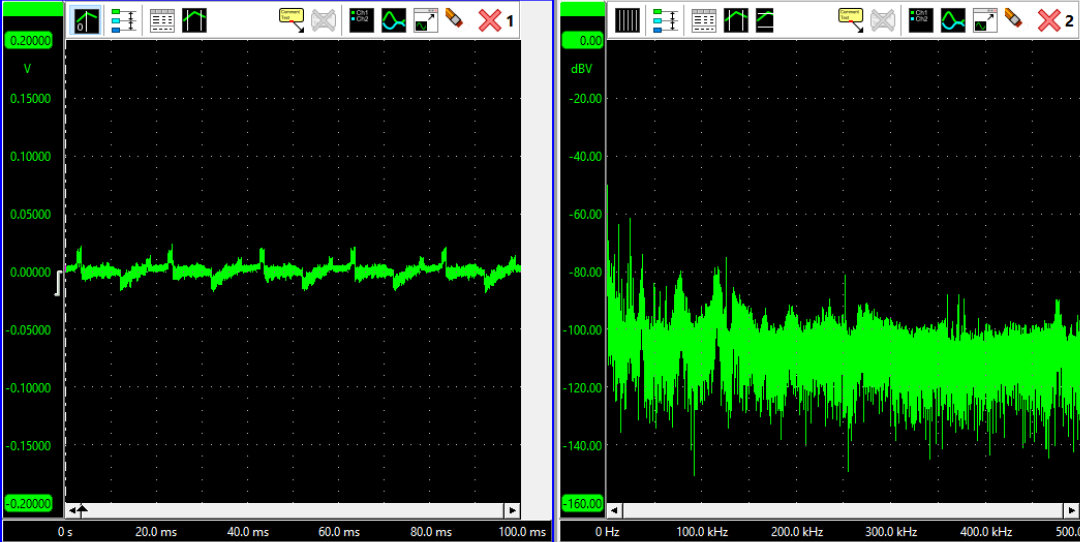

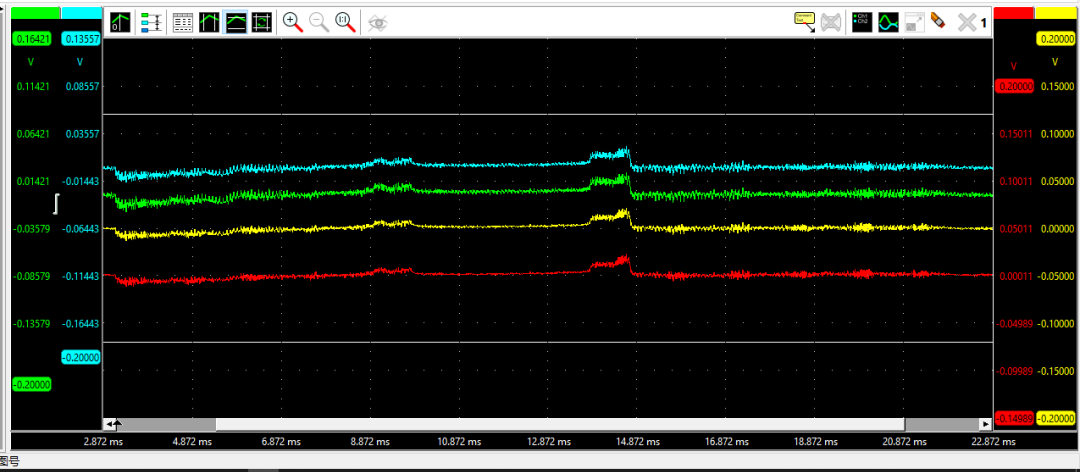

可以看到 FFT 的功能很准,这是非常好的。信号源是泰克的:

这东西好像三四万,真贵。。。

这东西好像三四万,真贵。。。

呜呜呜,又是老外的

呜呜呜,又是老外的

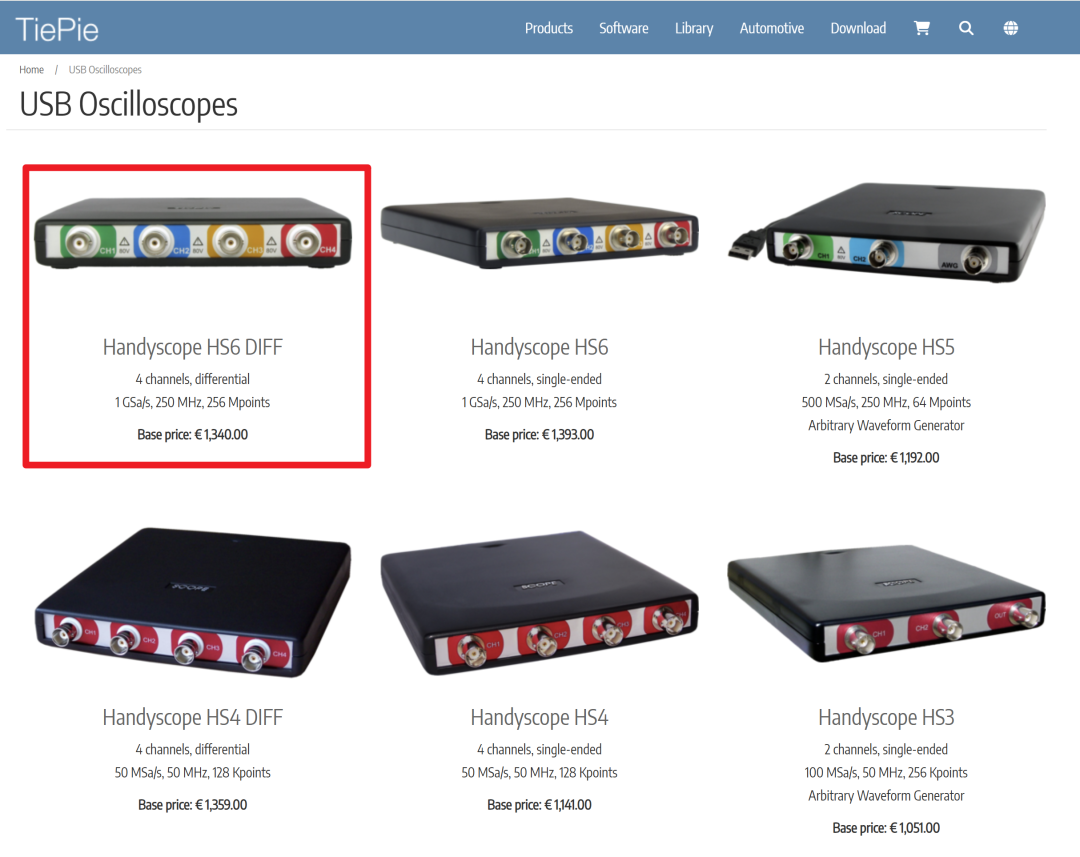

然后系列是 USB 示波器,然后我拿到的是性能最好的

然后系列是 USB 示波器,然后我拿到的是性能最好的

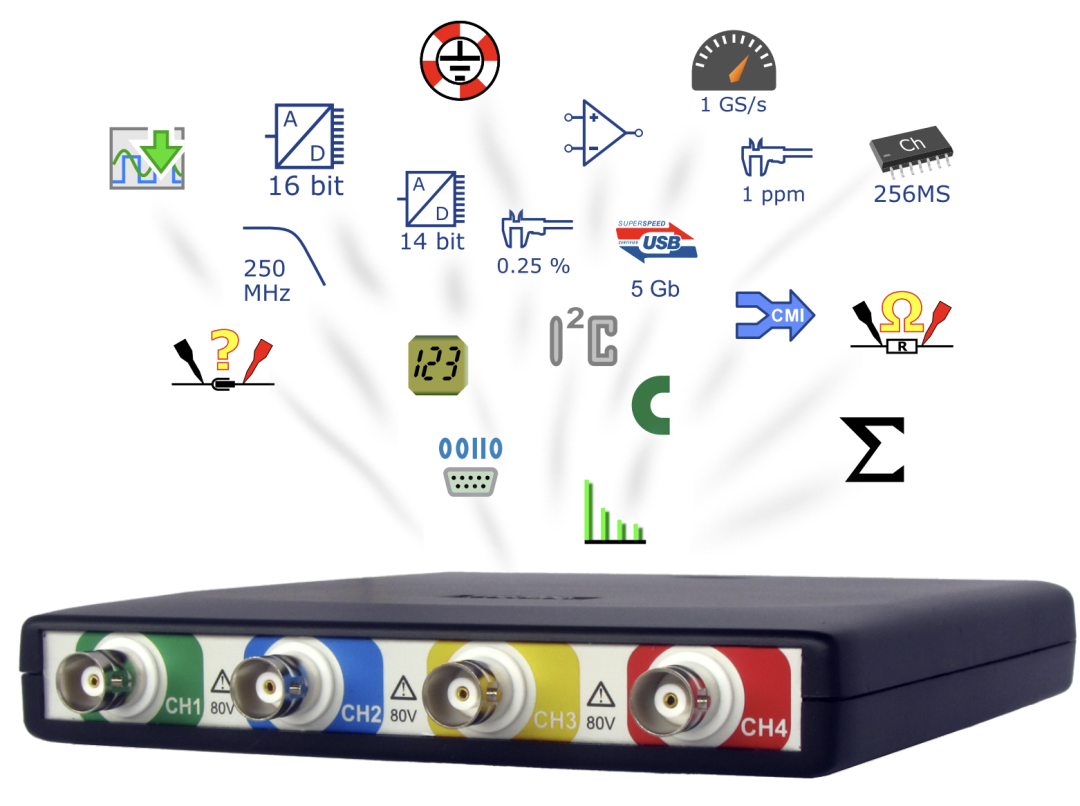

这个展示图是比较形象的说明了示波器的功能

这个展示图是比较形象的说明了示波器的功能

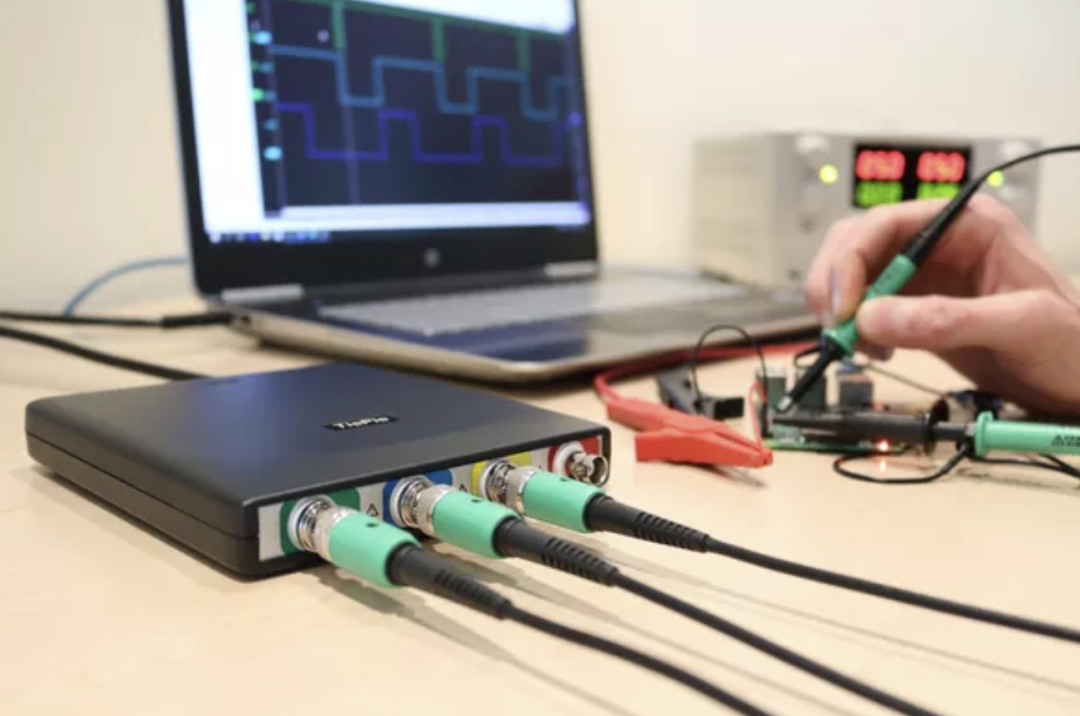

用的时候直接这样摆桌子上面

用的时候直接这样摆桌子上面

也可以通过同步线互相连接

也可以通过同步线互相连接

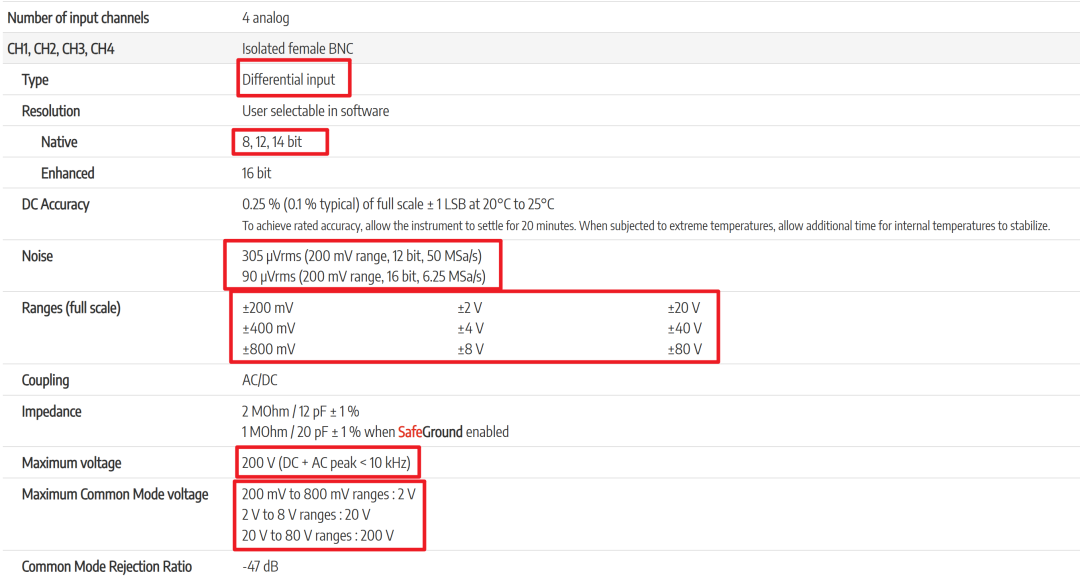

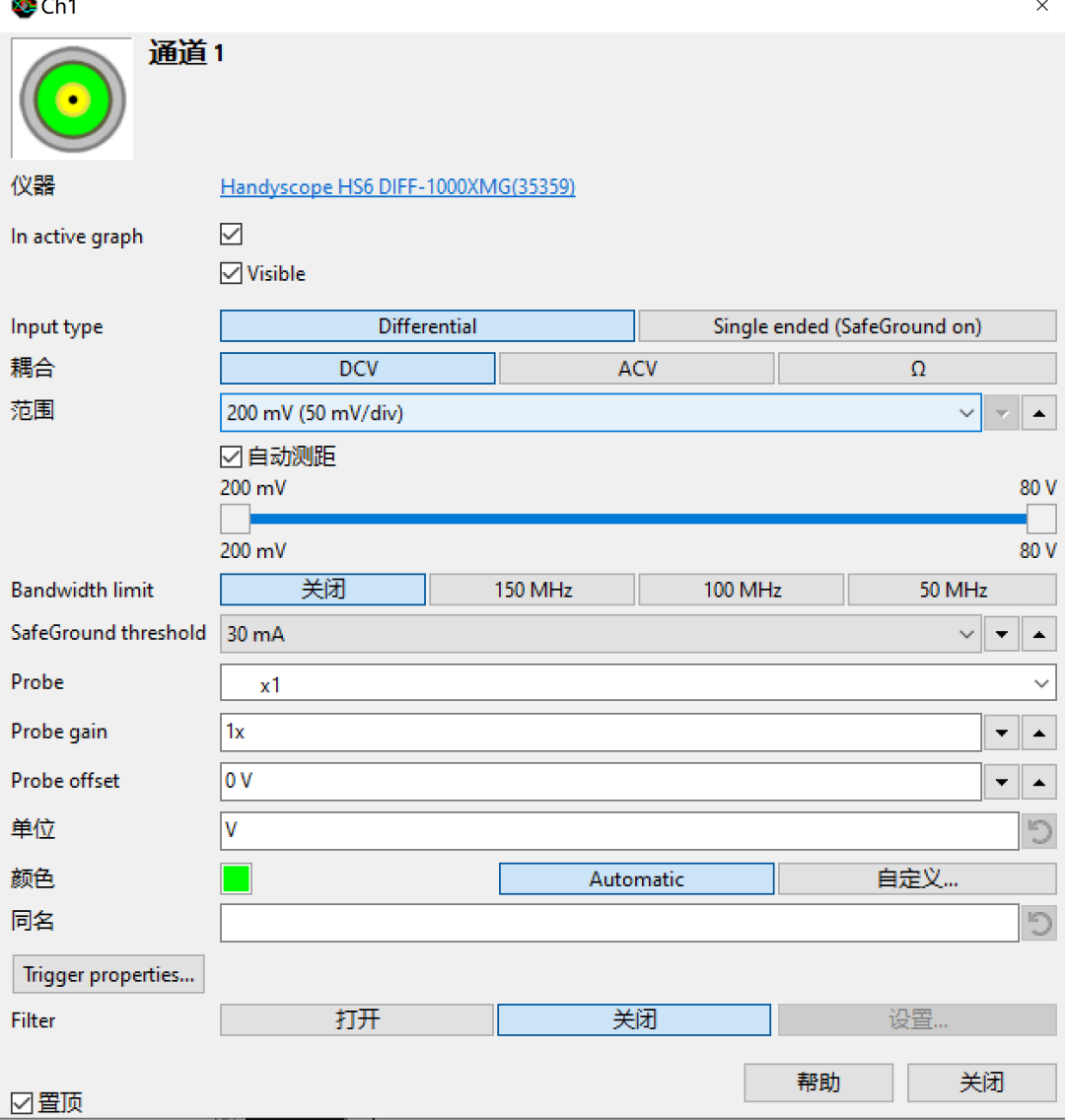

测量方式是差分的

测量方式是差分的

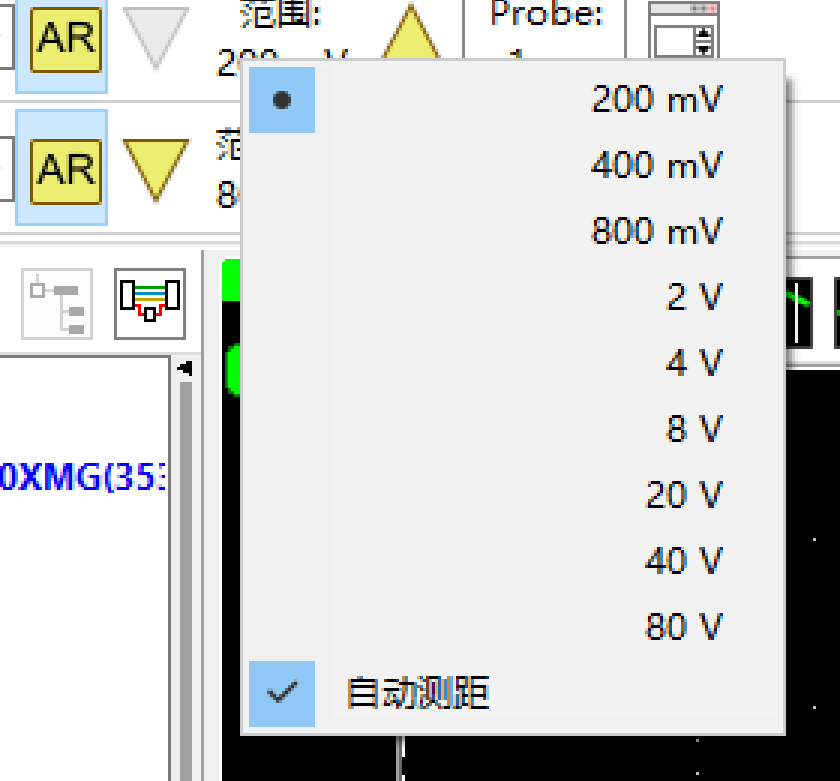

也可以单端接地测试,可以通过过采样到 16bit 去进行高精度测量,测试的档位很多,覆盖大多数的测试范围。

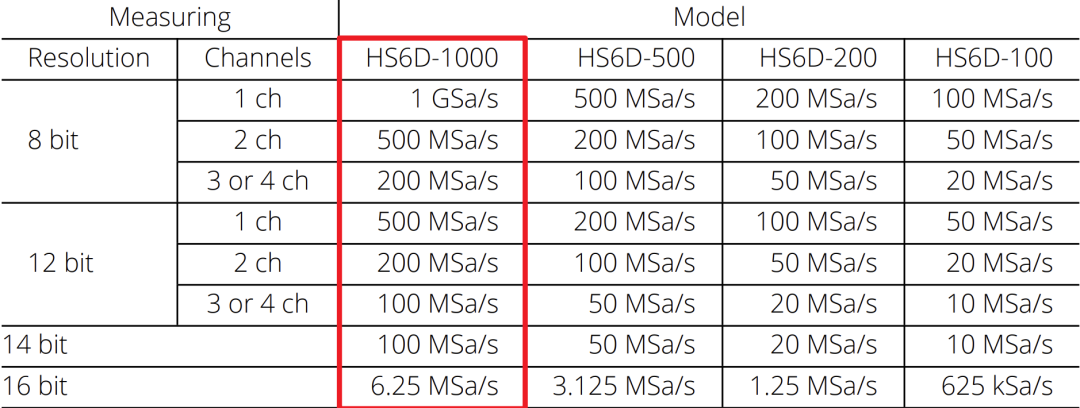

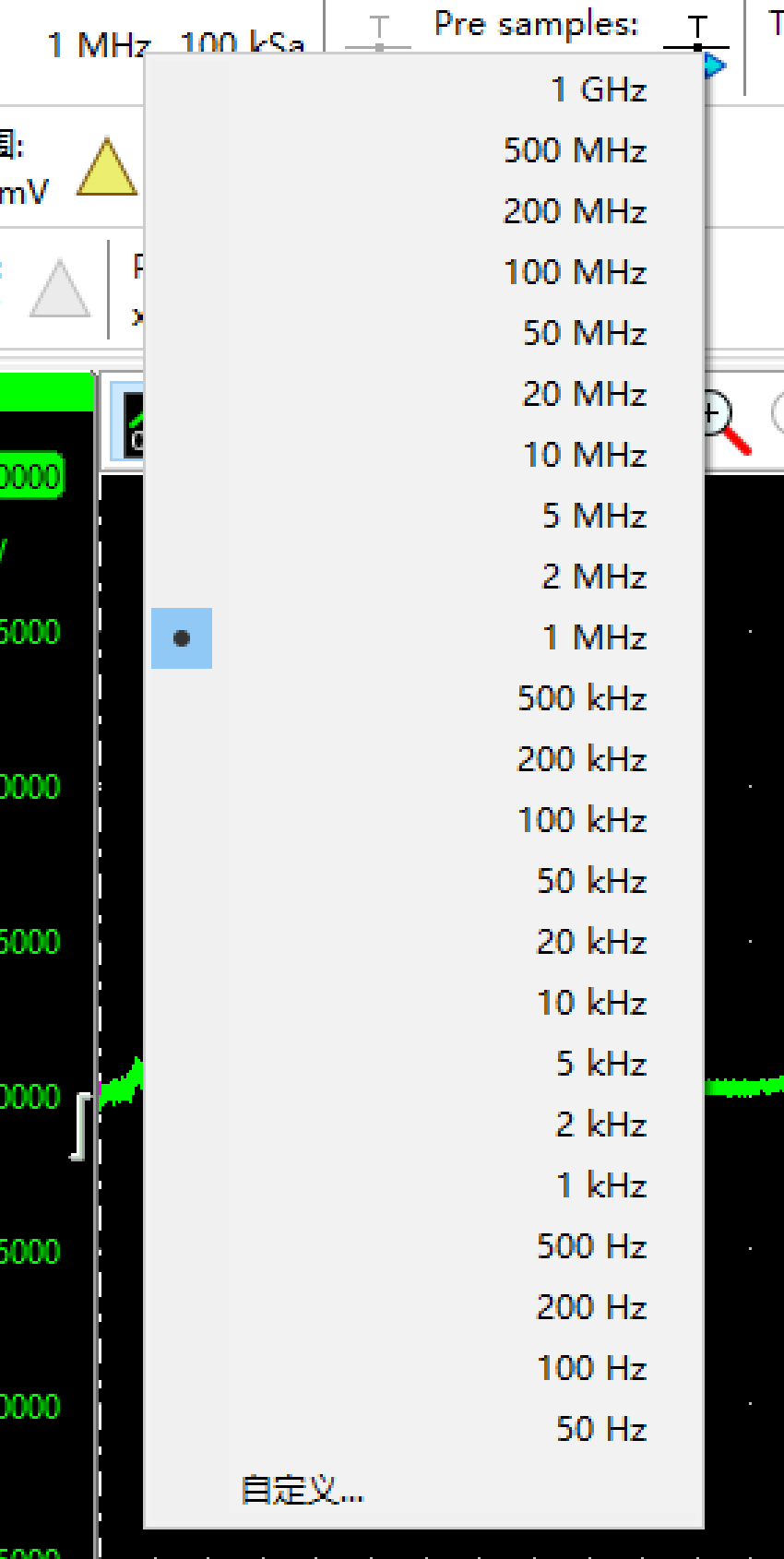

最高可以做到 1G 的采样率

最高可以做到 1G 的采样率

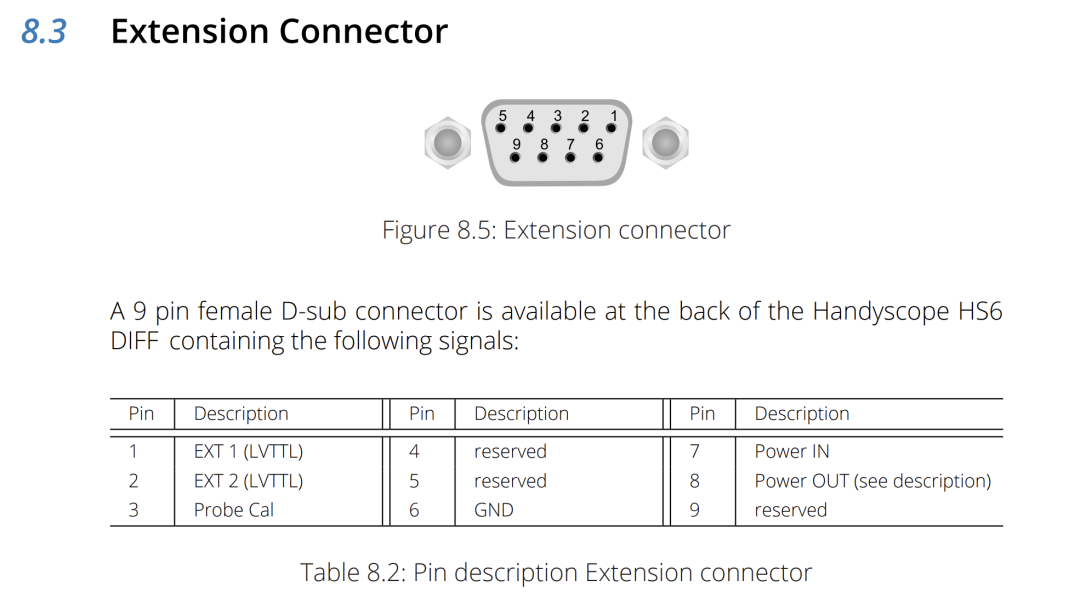

后面有一个 RS232 的接口,可以和其它的仪器联动

后面有一个 RS232 的接口,可以和其它的仪器联动

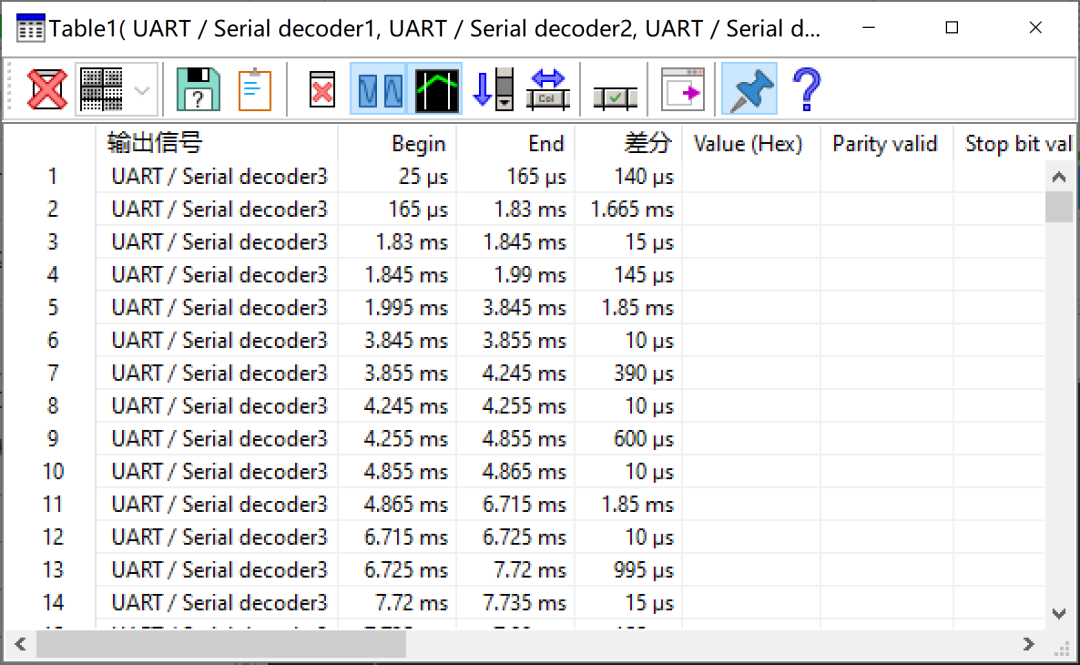

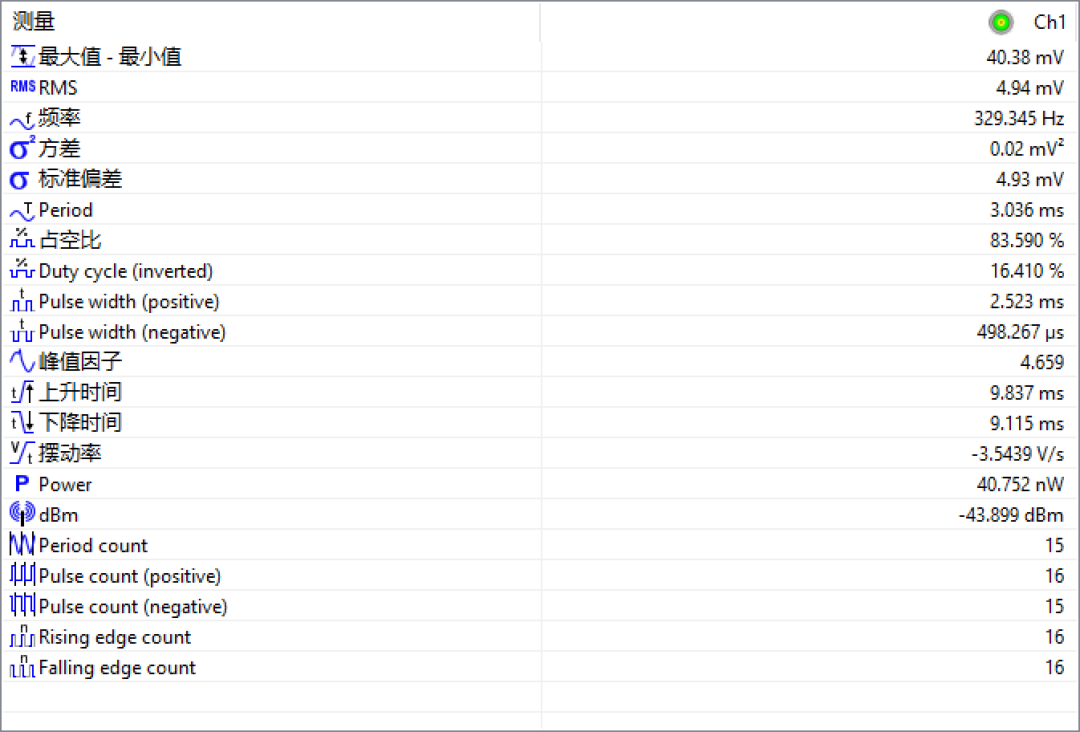

这个是输出的数据

这个是输出的数据

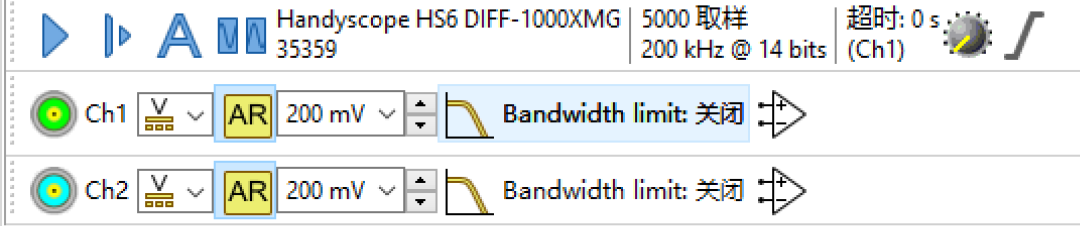

看看上位机

仪器是自动连接的:

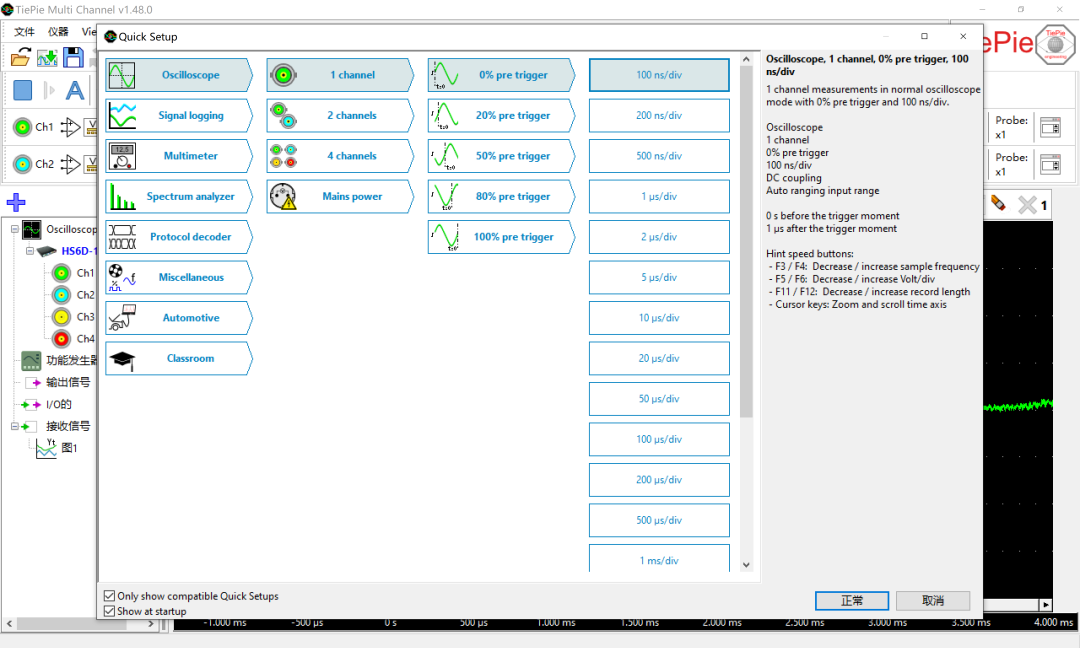

每次都会问你要使用什么功能

每次都会问你要使用什么功能

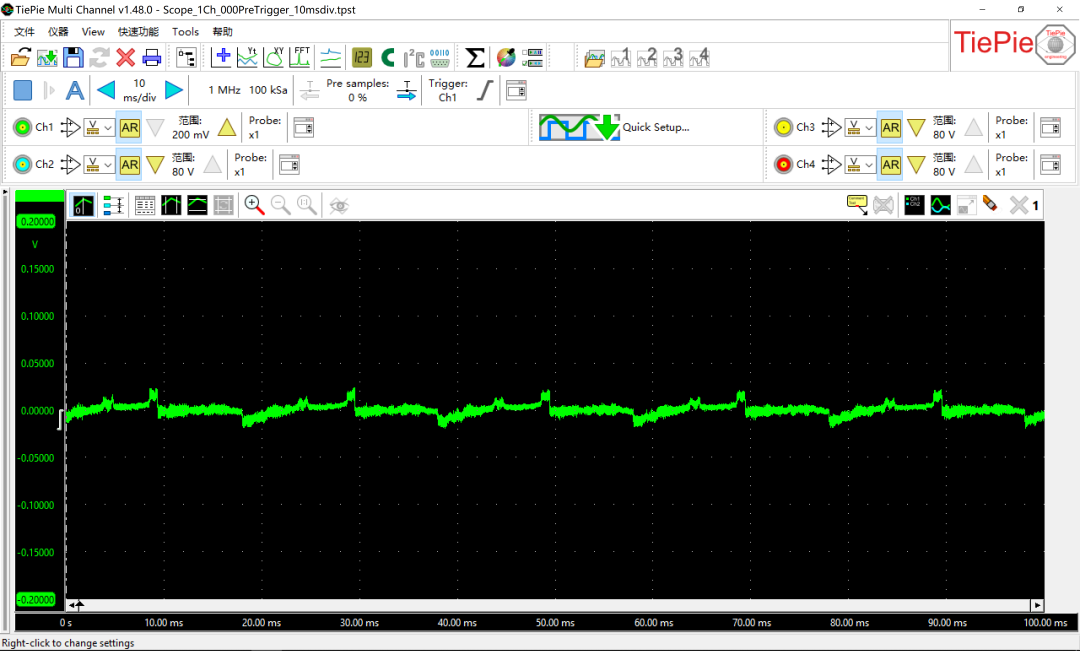

然后映入眼帘的是一个简约的 UI

然后映入眼帘的是一个简约的 UI

可以点击每个通道进行详细的设计

可以点击每个通道进行详细的设计

我习惯使用自动模式

我习惯使用自动模式

采样 1M 是比较合适的,等完全对信号了解了可以再微调

采样 1M 是比较合适的,等完全对信号了解了可以再微调

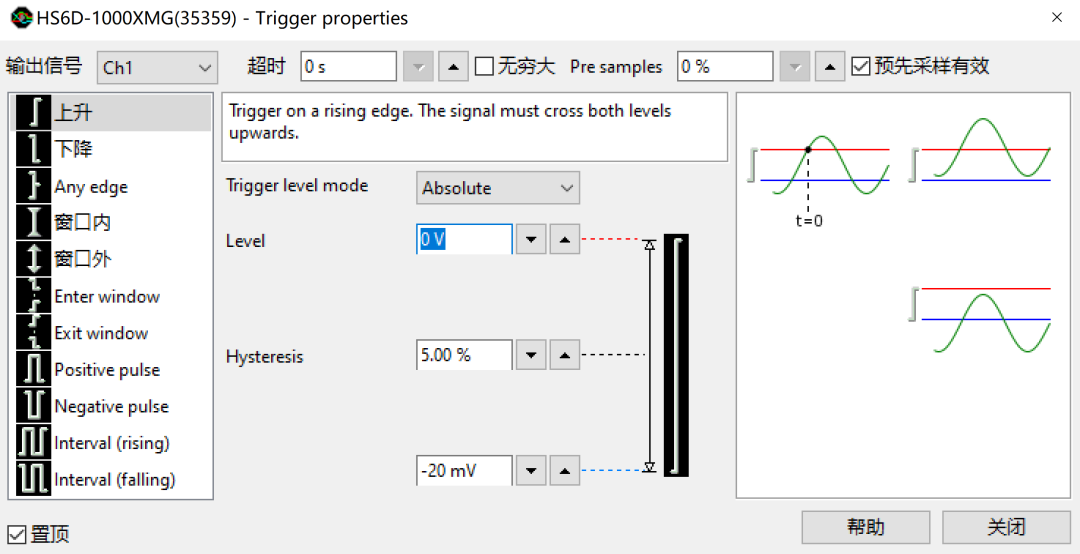

没有普通示波器的触发功能多

没有普通示波器的触发功能多

提供了详细的测试计算数据

提供了详细的测试计算数据

当然是可以指定开启的

当然是可以指定开启的

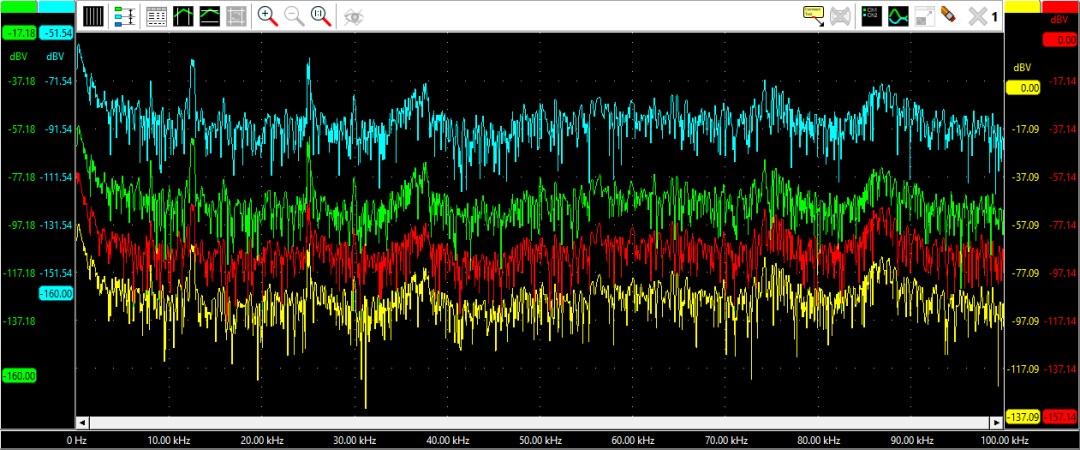

可以自由的添加图窗,我习惯看 FFT

可以自由的添加图窗,我习惯看 FFT

也可以打开高级模式

也可以打开高级模式

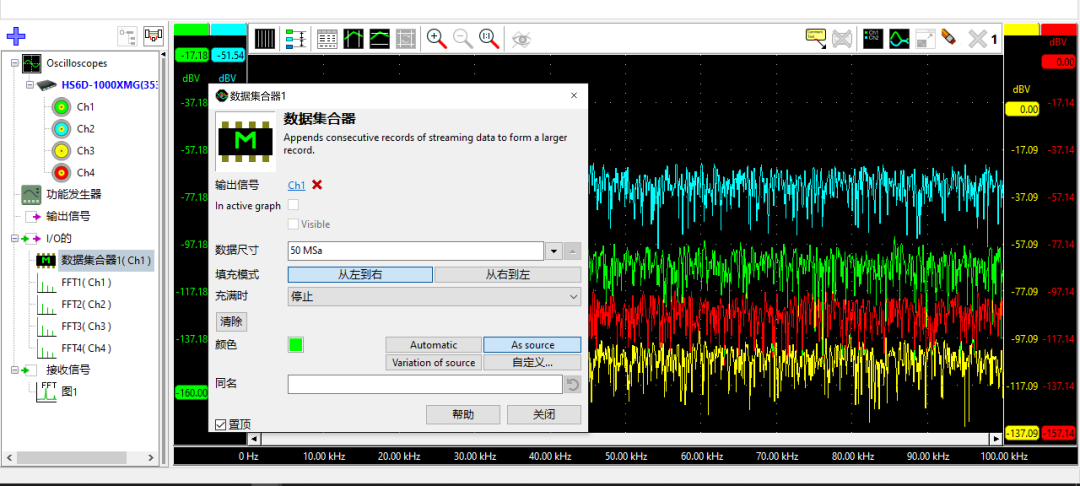

这个我得夸夸,这个是就是水平系统的信号链设置,完全是不需要学习的,一眼就知道作用是什么,好评!!!

同步选择四路是可以的

同步选择四路是可以的

需要微调偏移,不然不好看。

FFT 也是可以的

FFT 也是可以的

这些数据也是可以同步设置的

这些数据也是可以同步设置的

在左边,可以任意的将数据做计算,流式的串联处理。

内部设计

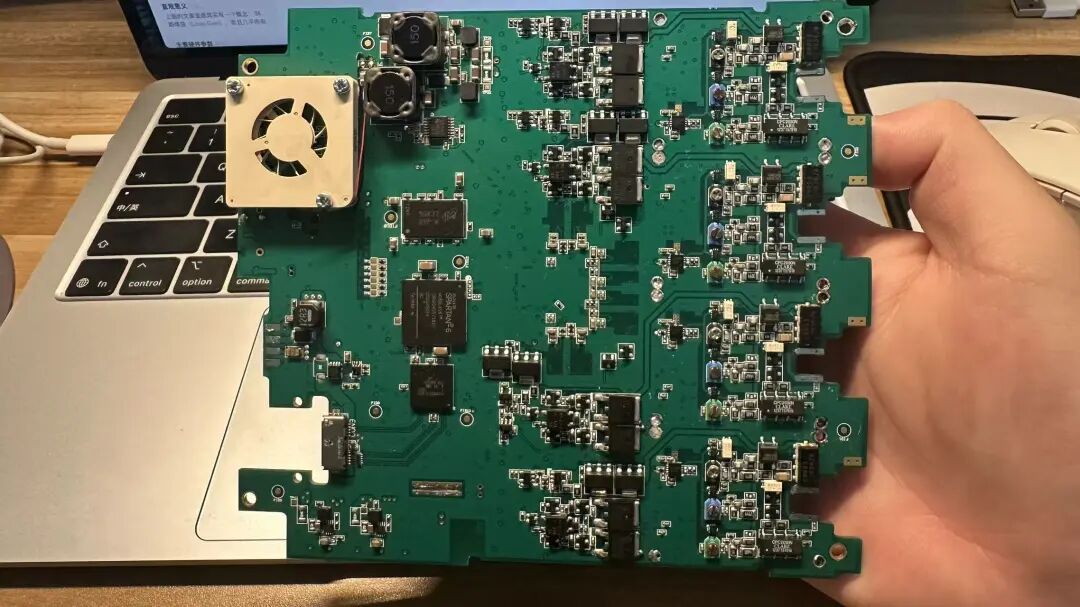

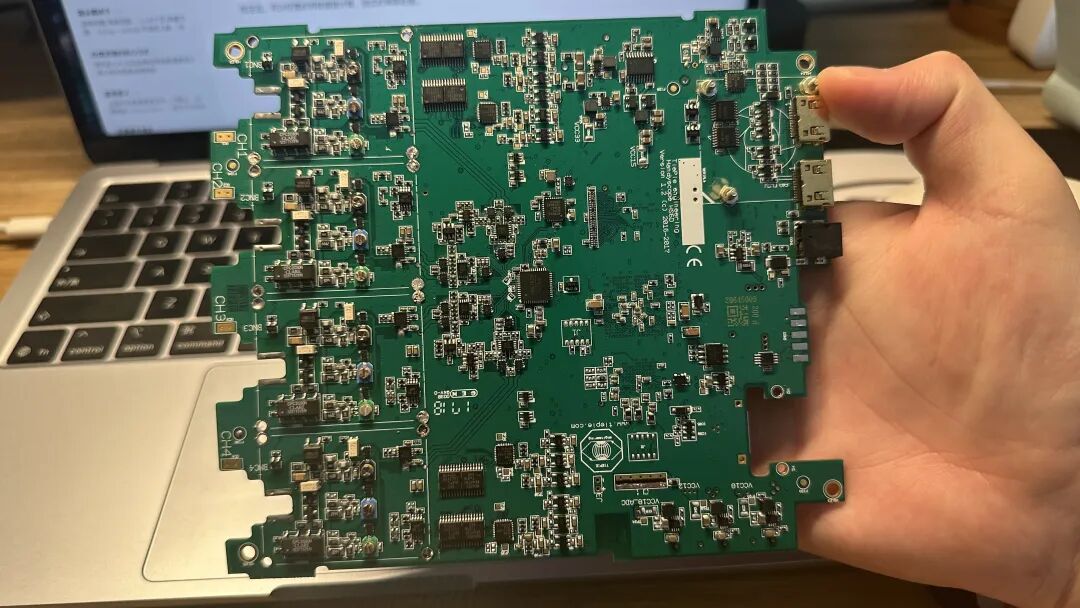

那这么强大的功能,如何实现?仇老板棒棒,然后也给我准备了内部的板子:

正面

正面

强大的 FPGA 和塞浦拉斯的 USB,其它先不看:

正面是信号链系统

正面是信号链系统

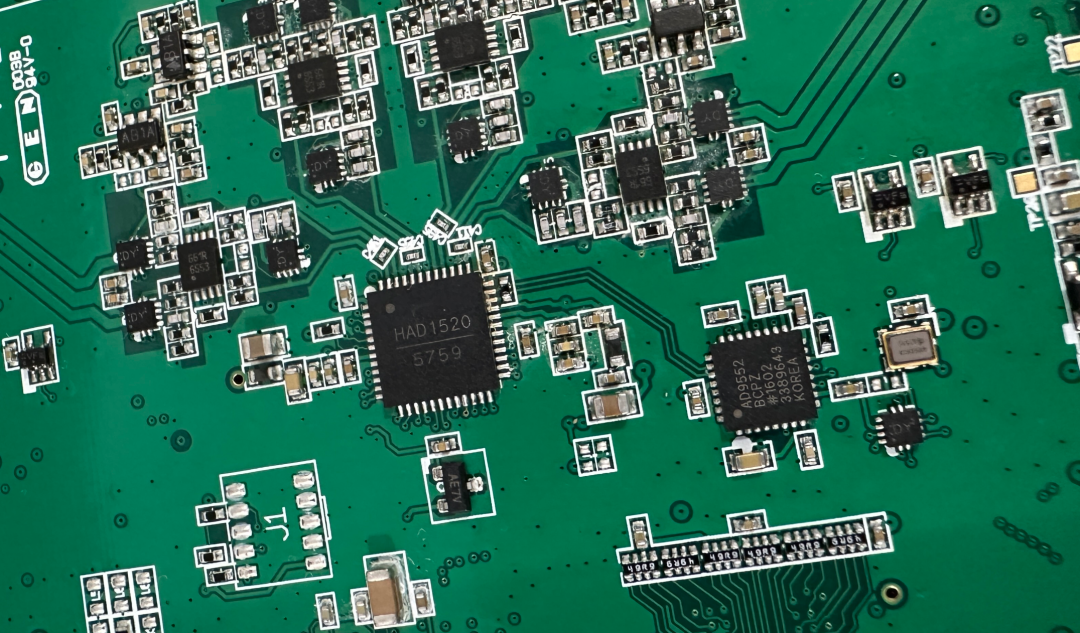

只有一个 ADC:

被 ADI 收购了

被 ADI 收购了

上面是 ADC+一个时钟

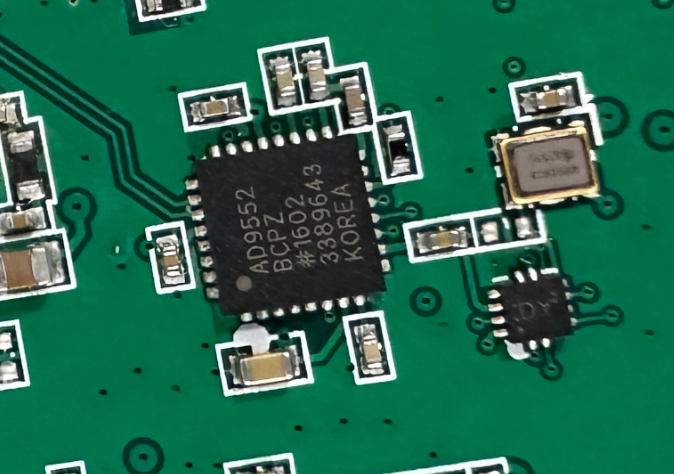

就是这颗

就是这颗

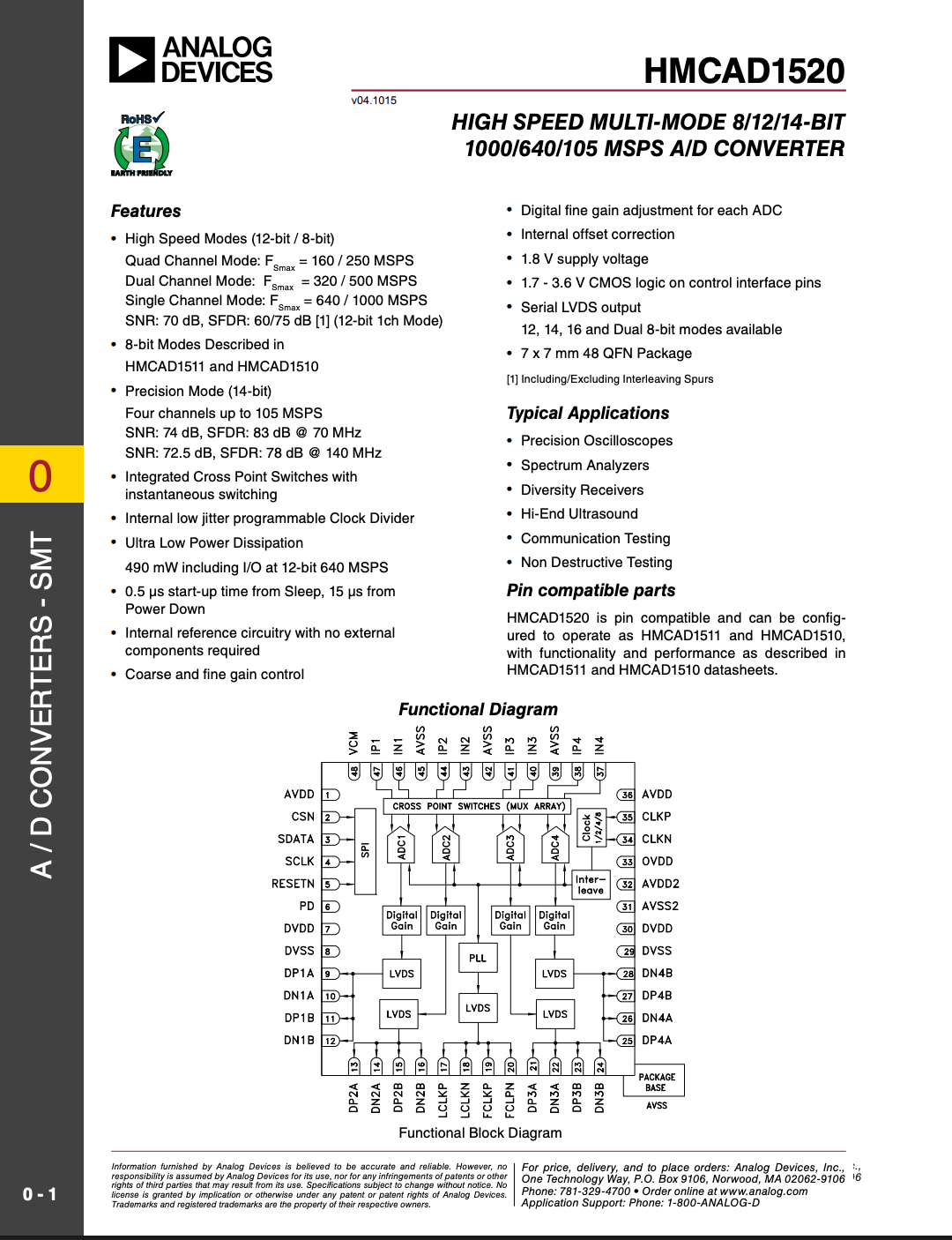

HMCAD1520 是 Analog Devices 出品的一款非常灵活、集成度高的 多模高速模数转换器(ADC)。

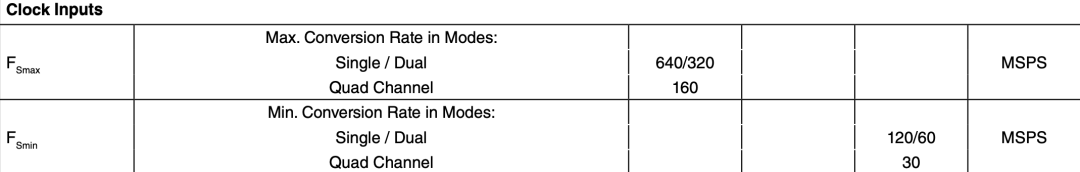

多模式高速 ADC

模式 | 通道数 | 分辨率 | 最高采样率 | 典型 SNR | 典型 SFDR |

|---|---|---|---|---|---|

单通道高速 | 1 | 12 bit | 1000 Msps | 70 dB | 75 dBc |

双通道高速 | 2 | 12 bit | 500 Msps | 70 dB | 77 dBc |

四通道高速 | 4 | 12 bit | 250 Msps | 70 dB | 78 dBc |

精密模式 | 4 | 14 bit | 105 Msps | 74 dB | 83 dBc |

可以通过 SPI 配置,让它“变身”为:

1 通道 1Gsps;

2 通道 500Msps;

4 通道 250Msps;或 4 通道高精度 14-bit 模式。

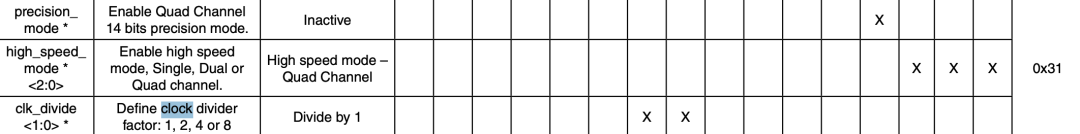

内部架构与工作原理

内部结构:8 个子 ADC 分支

在手册第 32 页明确指出:

“HMCAD1520 is a Multi-Mode high-speed CMOS ADC, consisting of 8 ADC branches, configured in different channel modes, using interleaving to achieve high speed sampling. For all practical purposes, the device can be considered to contain 4 ADCs.”

也就是说:

物理上有 8 个子 ADC(branch)。

逻辑上表现为 4 个 ADC 通道(Channel 1~4)。

通过 时分交错(interleaving) 来提升采样率。

模式下子 ADC 的使用方式

模式 | 有效通道数 | 每通道使用的子 ADC 数 | 最大采样率 | 说明 |

|---|---|---|---|---|

Quad Channel Mode | 4 | 各用 1 个 branch | 160 MSPS | 无交错,每个通道独立一个子 ADC |

Dual Channel Mode | 2 | 各用 4 个 branch | 320 MSPS | 每个通道交错 4 个 branch |

Single Channel Mode | 1 | 使用全部 8 个 branch | 640 MSPS / 1000 MSPS | 8 × 交错合成高速输出 |

Precision Mode | 4 | 各用 1 个 branch | 105 MSPS | 不交错,14 位高精度模式 |

内部结构示意理解

┌──────────────┐

IN1 ───▶ │ ADC1 branch │──┐

IN2 ───▶ │ ADC2 branch │──┼─> 组合为 Channel 1(Dual 模式时)

IN3 ───▶ │ ADC3 branch │──┤

IN4 ───▶ │ ADC4 branch │──┘

│ │

IN5 ───▶ │ ADC5 branch │──┐

IN6 ───▶ │ ADC6 branch │──┼─> 组合为 Channel 2

IN7 ───▶ │ ADC7 branch │──┤

IN8 ───▶ │ ADC8 branch │──┘

└──────────────┘

交错方式:每个 branch 依次采样不同时间相位(时钟偏移),合成一个高采样率数据流。

芯片内部实际上有 8 个 pipeline ADC branch;不同模式下,这些分支被交错(interleaving)使用来提升采样率:

Quad 模式 → 4 通道并行;

Dual 模式 → 每个通道 4 路交错;

Single 模式 → 所有 8 路交错,达到最高速。

交错采样的好处:用多路较慢 ADC 组合成一个更高速的虚拟 ADC;节省功耗和面积。

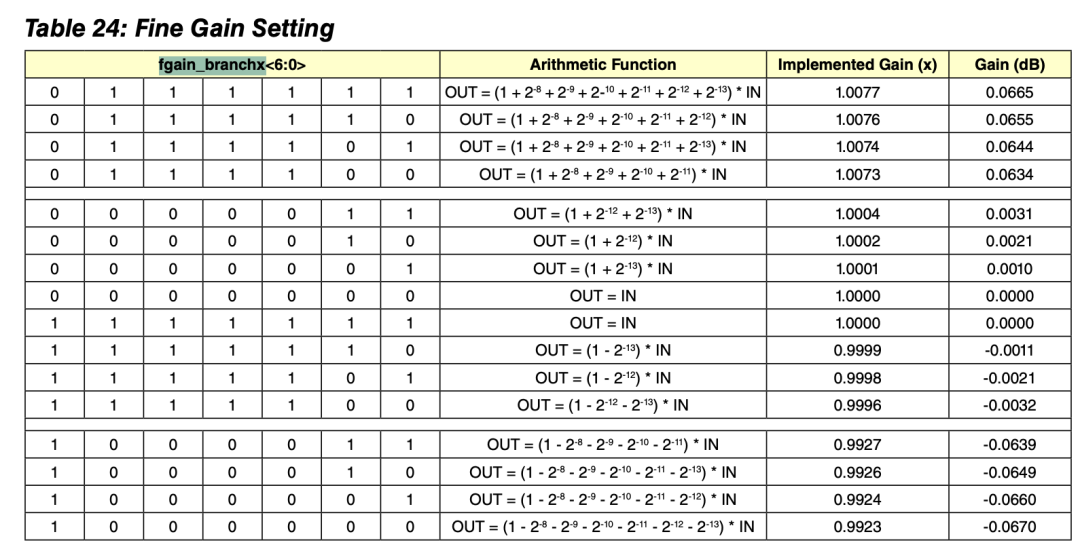

潜在问题:分支之间增益、偏移、时序不完全一致,会产生“交错噪声”(spur);芯片内置 Fine Gain 校准寄存器(fgain_branchX)用于补偿。

这个

这个

ADC 架构类型:Pipeline 型

每一级处理若干位精度,再将残差信号传递到下一级;最终通过数字误差校正逻辑合成高精度输出。

无缺码(No missing codes)

高线性度(INL ±0.6 LSB)

适合中高速高分辨率应用(>100 Msps)

参考电压与输入范围

内部 1 V 差分基准(无需外部参考)

差分输入范围:±1 V(共模 0.9 V)

内部提供 VCM 输出引脚(0.5×AVDD ≈ 0.9 V)作为输入参考

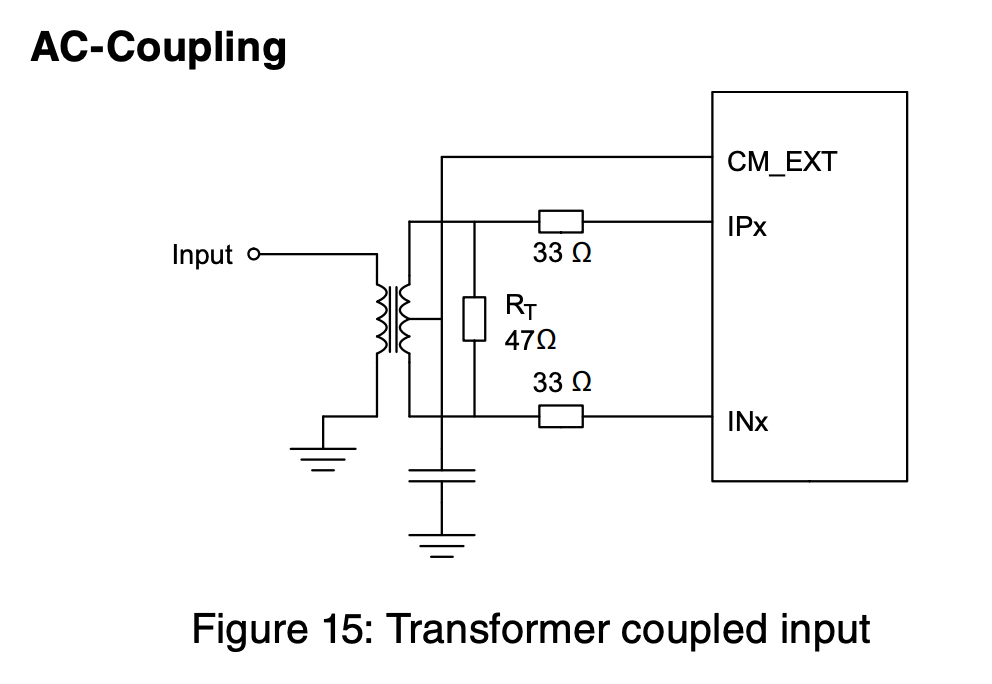

输入方式:

直流耦合 (DC coupling):输入放大器驱动差分;

交流耦合 (AC coupling):变压器或电容耦合方式;

推荐差分输入阻抗:43 Ω + 33 pF(滤除瞬态)。

手册里面都有

手册里面都有

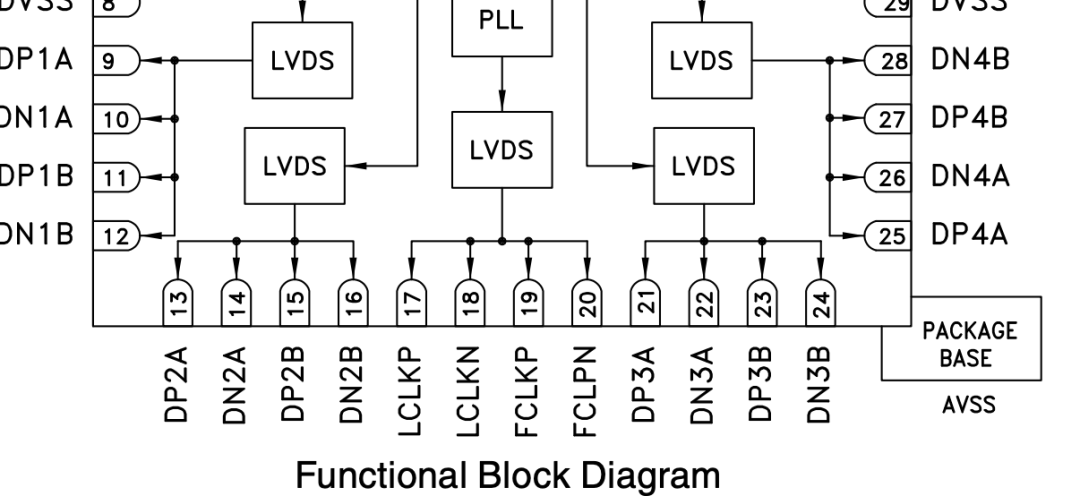

数字接口与时序

输出接口:LVDS (差分高速串行输出)

必须 FPGA

必须 FPGA

支持 8、12、14、16-bit、Dual 8-bit 输出格式;

最高数据速率:1 Gb/s;

带帧时钟 (FCLK)与位时钟 (LCLK);

可调输出相位(phase_ddr)、提前/延迟一个比特周期(lvds_advance / delay)。

在 FPGA 里接收时,只要对齐 FCLK 即可还原数据流。

内部时钟系统

image-20251017113954005

image-20251017113954005

单一差分时钟输入(支持 LVDS/LVPECL/sine/CMOS);内部可编程 **时钟分频器 (Clock Divider)**:÷1, ÷2, ÷4, ÷8

这个手册也写的有点粗略

这个手册也写的有点粗略

可在不同模式下维持同一个输入时钟源;

极低抖动 (Jitter):典型 120 fs rms;

上电启动时间:从休眠 0.5 µs;从掉电 15 µs。

功耗表现

模式 | 功耗(典型) |

|---|---|

单通道 640 Msps | 490 mW |

精密 105 Msps | 603 mW |

休眠模式 | 66 mW |

全掉电 | 15 µW |

这在 1Gsps / 12-bit ADC 级别中非常优秀。

寄存器配置逻辑(SPI)

SPI 采用 24-bit 帧结构:

[7:0] → 寄存器地址

[15:0] → 数据

例如:

操作 | 地址 | 数据 | 说明 |

|---|---|---|---|

复位 | 0x00 | 0x0001 | 软件复位 |

设置精密模式 | 0x31 | 0x0008 | 开启 14-bit 模式 |

设置 LVDS 输出为 14bit | 0x53 | 0x0002 | 精密模式推荐 |

选择输入 1→ADC1 | 0x3A | 0x0202 | 通道选择 |

启动运行 | 0x0F | 0x0000 | Power Down 拉低 |

信号路径与延迟

管线延迟 (Pipeline delay):

Quad 模式:32 个时钟;

Dual 模式:64;

Single 模式:128;

Precision 模式:15;因此当采样时,输入信号与数字输出之间会有固定延迟。

可编程低抖动时钟发生器

image-20251017113040190

image-20251017113040190

AD9552 = 可编程低抖动时钟发生器 / PLL 频率倍频器;用来把一个低频参考时钟(晶振、外部参考)转换成一个高频、低抖动的采样时钟。

在系统中:

HMCAD1520 需要一个稳定、干净的高速时钟(如 1 GHz、500 MHz、250 MHz);普通晶振(19.2 MHz / 20 MHz / 26 MHz)频率太低,不够直接驱动;AD9552 就是中间的“倍频器 + PLL + 抖动清理器”,负责把晶振变成超低抖动的高速时钟信号。

AD9552 的基本原理

它是一个 Fractional-N PLL(分数-N 锁相环)时钟发生器,内部结构如下:

外部晶振 / 参考时钟

│

[输入选择器]

│

▼

[分频 + 2×倍频模块]

│

▼

[Σ-Δ 分数N PLL + VCO + 环路滤波]

│

▼

[可编程分频器 P0 / P1]

│

├── OUT1 → 高速 LVDS/LVPECL 输出

└── OUT2 → 可为副输出或参考复制

工作范围

项目 | 数值 |

|---|---|

参考输入频率 | 6.6 MHz ~ 112.5 MHz |

输出频率范围 | 0 ~ 900 MHz |

内部 VCO 范围 | 3.35 GHz ~ 4.05 GHz |

输出逻辑 | LVDS / LVPECL / CMOS |

RMS 抖动 | < 0.5 ps(典型) |

电源 | 单 3.3 V,功耗约 400 mW |

在 HS6D-1000 系统中的作用

系统结构概念图

[高精度晶振 19.44 MHz]

│

▼

AD9552 低抖动时钟PLL

│

┌────┴────┐

▼ ▼

FPGA 时钟 HMCAD1520 采样时钟

(1G / 500M / 250M)

AD9552 负责:将 19.44 MHz 晶振倍频至 1 GHz;同时提供 FPGA 的逻辑参考时钟;输出为 LVDS 差分格式,与 ADC 的时钟输入直接兼容;其 RMS 抖动 <0.5 ps,可保证 ADC 的 ENOB 不被破坏。

AD9552 + HMCAD1520 搭配关系

模块 | 功能 | 信号电平 | 对应管脚 |

|---|---|---|---|

AD9552 | 时钟发生器 | LVDS 输出 | OUT1+, OUT1– |

HMCAD1520 | ADC 主采样时钟输入 | LVDS 输入 | CLK+, CLK– |

它们在板上通常用 100 Ω 差分匹配线直接相连; → 即 “AD9552 OUT1 → HMCAD1520 CLKIN”。

AD9552 的 锁相环 (PLL) 会把低频晶振锁定并倍频生成干净的时钟;这样整个采样系统的时钟噪声极低,采样精度最高。

AD9552 输出支持三种逻辑标准:

模式 | 电平摆幅 | 适用场景 |

|---|---|---|

LVDS | ±350 mV | 高速ADC(如HMCAD1520) |

LVPECL | ~800 mV | 高速逻辑/驱动远端 |

CMOS | 3.3 V | 低速逻辑或调试信号 |

HS6D-1000 实际上选择 LVDS 模式(差分对称、低噪声)。

“低抖动”到底多厉害?

输出抖动:0.47 ps rms(12 kHz~20 MHz);

对比普通晶振倍频器(几 ps rms),AD9552 的性能可提升 ADC ENOB 0.5–1 bit;

这对 12-14 bit、1 Gsps 采样系统非常关键;抖动越低,ADC 的信噪比 (SNR) 越高:

例如输入 100 MHz 正弦波,0.5 ps 抖动对应的时钟限制 SNR ≈ 80 dB;如果时钟抖动是 5 ps,SNR 立刻降到 60 dB。

组合后构成:

高分辨率差分采集系统 = AD9552(时钟) + HMCAD1520(ADC) + FPGA(数字控制)

后记

这个东西好好哦,硬件也就是一颗 ADC,然后软件设计的好好;软件还有有光明的未来。

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-10-17,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录