从微体系结构中提取的x86程序计数器?

我正在读“RISC-V阅读器:开放架构地图集”一书。为了解释ISA (指令集体系结构)与特定实现(即微体系结构)的隔离,作者写道:

架构师的诱惑是在ISA中包含一些指令,这些指令可以帮助在特定时间实现一个实现的性能或成本,但却负担不同的或未来的实现。

据我所知,在设计ISA时,ISA应该避免公开实现它的特定微体系结构的细节。

记住上面的引语:当谈到程序计数器时,在RISC上,程序计数器(pc)指向当前正在执行的指令。另一方面,在x86 ISA上,程序计数器(eip)不包含当前正在执行的指令的地址,而是包含当前指令后面的一个的地址。

是否将x86程序计数器从微体系结构中抽象出来?

回答 1

Stack Overflow用户

发布于 2019-07-23 21:33:56

我将用MIPS而不是x86来回答这个问题,因为(1) MIPS和x86在这方面有相似之处,而且(2) RISC V是由Patterson等人在使用MIPS的几十年经验之后开发的。我觉得他们的书中的这些语句最好在这个比较中理解,因为x86和MIPS都是相对于指令末尾的代码分支偏移量(pc+4 in MIPS)。

在MIPS和x86中,PC相关寻址模式只出现在早期ISA版本的分支中.后来的修订增加了PC相对地址的计算(例如,MIPS、auipc或x866-64的LEA或load/store的相对寻址模式)。所有这些都是一致的:偏移量是相对于指令的结尾(即下一个指令开始)编码的,而正如您注意到的,在RISC V中,编码的分支偏移量(和auipc等)。相对于指令的开始。

它的价值在于它从某些数据路径中删除了一个加法器,有时其中一个数据路径可能位于关键路径上,因此对于某些实现来说,数据路径的这种微小的缩短意味着更高的时钟速率。

(RISC V当然仍然需要为pc生成指令+4-next和呼叫指令的返回地址,但关键路径上的指令地址要少得多。请注意,在下面的图表中,这两种方法都没有显示捕获pc+4作为返回地址。)

让我们比较一下硬件框图:

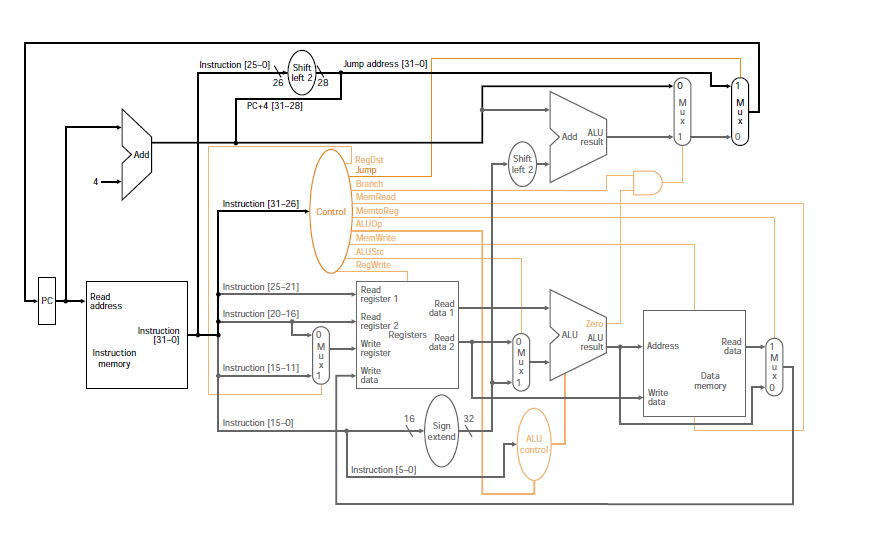

MIPS数据路径(简化)

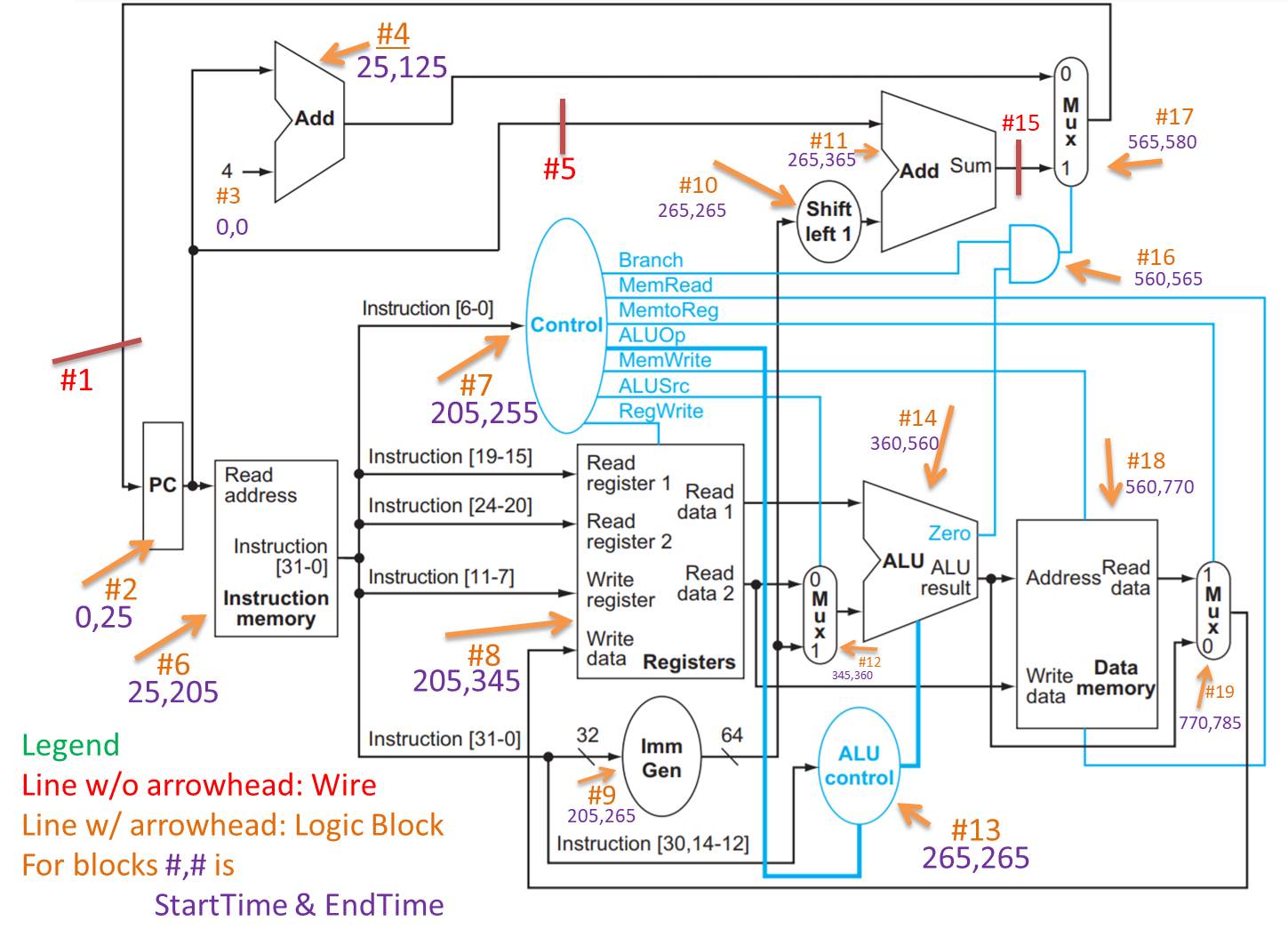

RISC V数据路径(简化)

您可以在RISC V数据路径图上看到标记为#5的线(红色,刚好在控制椭圆上方),绕过加法器(#4,它将4添加到pc-next)。

图的属性

- MIPS:在向MIPS单周期数据路径添加功能时需要帮助?

- RISC V:https://www.codementor.io/erikeidt/logic-block-diagrams-w6zxr6sp6

为什么x86 / MIPS在最初的版本中做出了不同的选择?

当然,我不能肯定。在我看来,有一个选择是可以选择的,而对于最早的实现来说,这根本不重要,所以他们可能甚至都没有意识到潜在的问题。几乎每条指令都需要计算指令--无论如何,下一步,这似乎是合乎逻辑的选择。

充其量,他们可能已经节省了一些电线,因为pc-下一个确实是需要其他指令(例如呼叫)和pc+0不一定需要。

对以前的处理器进行检查可能会发现,这正是当时所做的事情,所以这可能更多地是对现有方法的继承,而不是一种设计选择。

8086不是流水线的(除了指令预取缓冲区外),可变长度的解码已经在指令开始执行之前找到了指令的结尾。

经过多年的回顾,这个数据路径问题现在在RISC V中得到了解决。

我怀疑他们对此做出的有意识的决定,就像对分支延迟时隙(MIPS)所做的那样。

根据注释中的讨论,8086可能没有任何推动指令开始地址的异常。与以后的x86模型不同,divide将指令地址推到div/idiv之后。在8086,中断-恢复后,cs rep movsb (或其他字符串指令)推送地址的最后一个前缀,而不是整个指令包括多个前缀。这个"bug“被记录在英特尔的8086手册(扫描PDF)中。所以很有可能8086真的没有记录指令开始地址或长度,只有解码在开始执行之前完成的地址。这个被固定至少286,也许是186个,但是适用于所有的8086 / 8088 CPU。

MIPS从一开始就有虚拟内存,因此它确实需要能够记录错误指令的地址,以便在异常返回之后重新运行。此外,软件TLB-漏处理也需要重新运行一个错误指令.但是异常速度很慢,无论如何都会刷新管道,并且在提取之后很长时间内才会被检测到,因此不管如何,大概都需要进行一些计算。

https://stackoverflow.com/questions/57171220

复制相似问题