使用JK触发器的同步计数器不像预期的那样工作。

使用JK触发器的同步计数器不像预期的那样工作。

提问于 2018-09-03 16:08:48

我试图在Sanir的"Verilog“一书中做一个练习:用JK触发器设计一个同步计数器。

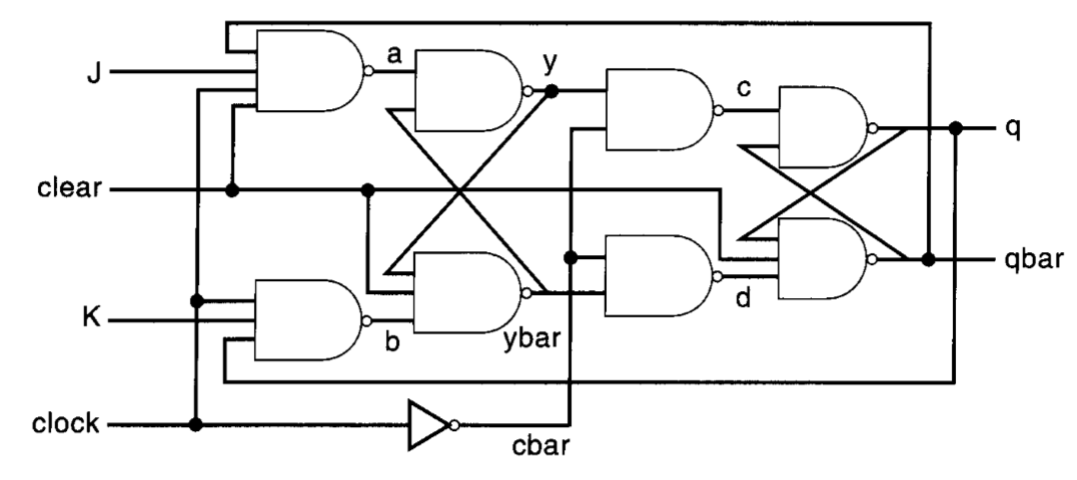

本书提供的JK触发器电路:

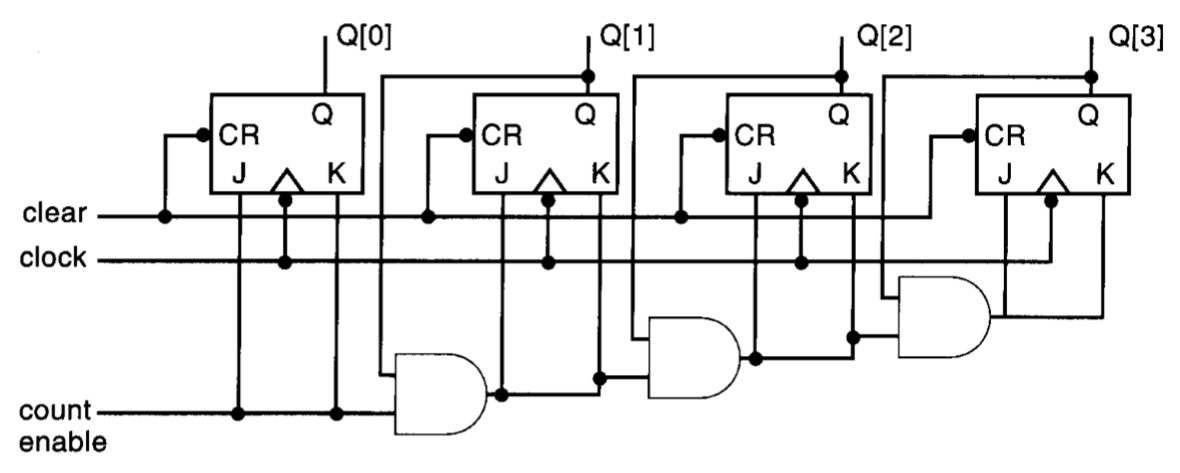

计数器电路:

我认为上面的电路有一个错误:输入到3和门应该分别是Q0,Q1,Q2,从左到右,而不是Q1,Q2,Q3。修改后,我编写了以下代码:

module verilogtest(clk, CS, q, clr);

input clk, CS, clr;

output[3:0] q;

counter count(clk, CS, q, clr);

endmodule

module counter(clk, CS, q, clr);

input clk, CS, clr;

output[3:0] q;

wire t1, t2, t3;

assign #1

t1 = CS & q[0],

t2 = t1 & q[1],

t3 = t2 & q[2];

mJKff ff1(q[0], CS, CS, clk, clr);

mJKff ff2(q[1], t1, t1, clk, clr);

mJKff ff3(q[2], t2, t2, clk, clr);

mJKff ff4(q[3], t3, t3, clk, clr);

endmodule

module mJKff(Q, J, K, clk, clr);

output Q;

input J, K, clk, clr;

wire

a, b, c, d, y, ybar, cbar, qbar;

assign #1

a = ~(qbar & J & clk & clr),

b = ~(clk & K & Q),

y = ~(a & ybar),

ybar = ~(y & clr & b),

c = ~(y & cbar),

d = ~(ybar & cbar),

cbar = ~clk;

assign #1

qbar = ~(Q & clr & d),

Q = ~(c & qbar);

endmodule我成功地使用Quartus II编译,并得到了一系列警告:

警告:时间分析是将一个或多个组合循环作为锁存进行分析。 警告:“保留所有未使用的引脚”设置尚未指定,并将默认为“作为输出驱动地”。 警告:已发现的引脚作为未定义的时钟和/或内存启用 警告:在时钟路径中发现7个节点,这些节点可能充当波纹和/或门控时钟--节点被分析为缓冲区,从而导致时钟倾斜。 警告:电路可能无法工作。检测到2条非操作路径被时钟"clk“锁定,时钟偏差大于数据延迟。有关详细信息,请参阅汇编报告。 警告:电路可能无法工作。检测到1条非操作路径被时钟"CS“锁定,时钟偏差大于数据延迟。有关详细信息,请参阅汇编报告。 警告:电路可能无法工作。检测到1条非操作路径被时钟"clr“锁定,时钟偏差大于数据延迟。有关详细信息,请参阅汇编报告。

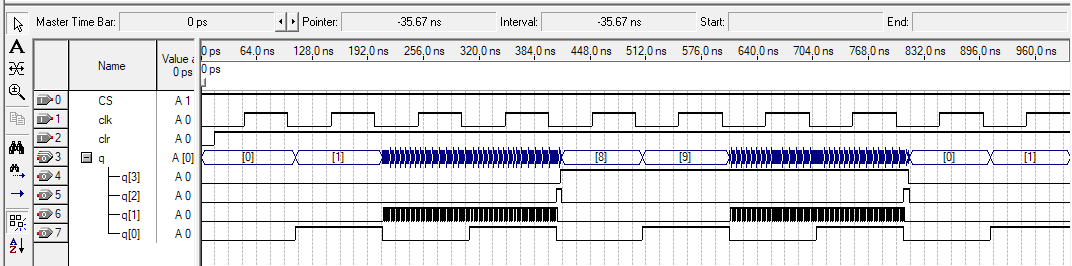

我认为最后三个警告是它不能工作的原因。仿真结果:

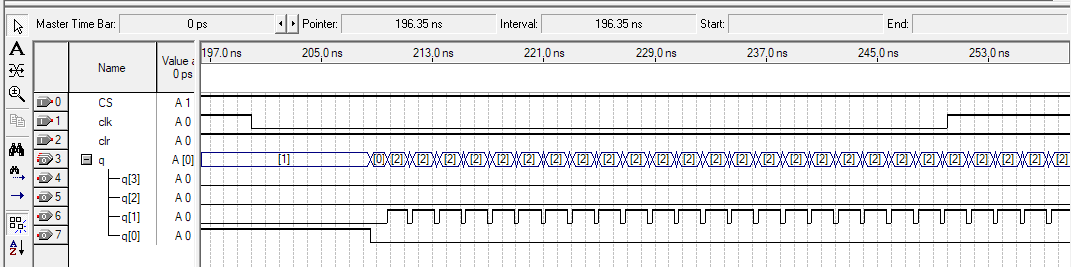

放大:

Q0的行为与预期相同,但其他的则不然。为什么?

回答 1

Stack Overflow用户

发布于 2018-09-05 19:11:00

您只是在连接计数器模块中的和门时有一个简单的错误:

assign #1

t1 = CS & q[0],

t2 = t1 & q[1],

t3 = t2 & q[2];应该是

assign #1

t1 = CS & q[1],

t2 = t1 & q[2],

t3 = t2 & q[3];Q[0]是唯一正确的输出,因为所有其他FF的JK输入都收到了错误的值。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/52153227

复制相关文章

相似问题