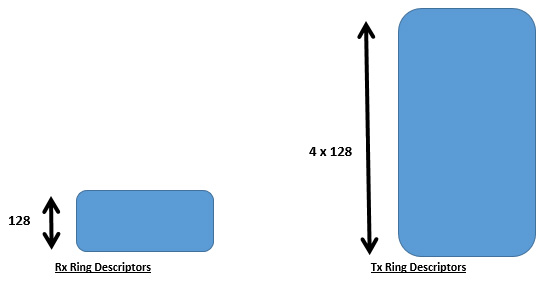

为什么TX描述符环的大小应该是RX描述符环大小的4倍?

为什么TX描述符环的大小应该是RX描述符环大小的4倍?

提问于 2017-09-18 12:42:58

回答 1

Stack Overflow用户

发布于 2018-05-22 19:29:01

你可以看到“传输缓冲区”在它下面。要修改描述符的数量,只需增加值。在我们的Windows系统中,限制是2048,必须是8的增量。在传输端,起始值为512,但2048乘以8的规则仍然适用。为什么TX比RX更多?我们的体系结构支持不确定的RX方面的优先级,因此描述符的周转率比TX端要高。此外,O/S有时无法及时将TX资产返回给驱动程序。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/46279589

复制相关文章

相似问题