Labview FPGA仿真时序

这是一个非常基本的问题。我无法模拟PWM文件,在系统时间,从它的FPGA VI文件。

详细信息

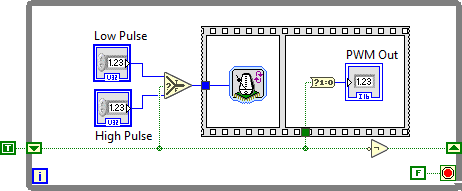

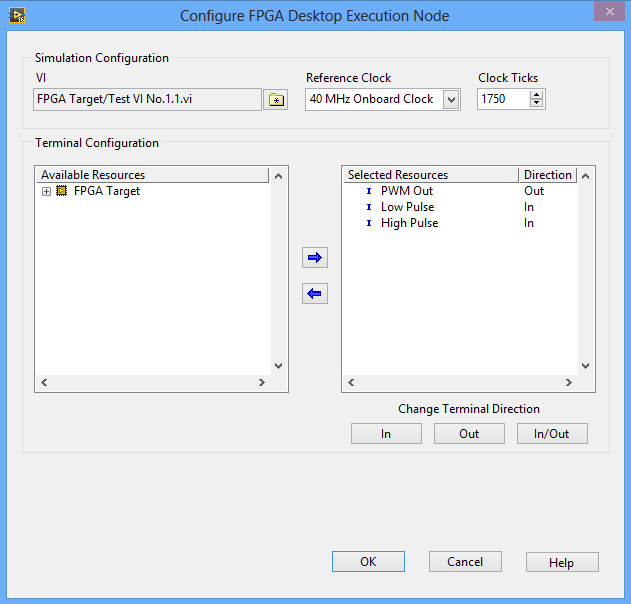

对于NI cRIO-9067 + LabVIEW 2016 + Windows 8系统,在FPGA接口模式下,我有测试VI编号1.vi NI LabVIEW文件和相应的FPGA桌面执行节点代码块文件Test VI NI.1 DEN.vi,如入门信息[1] [2]中所建议的那样。

在这两个文件中,低脉冲和高脉冲数字控件都填充了1000值。循环计时器块被设置为"mSec“计数器单元和内部计数器的"32位”大小。

编译后的第一个文件的FPGA版本在7分钟的本地编译后,每1秒执行一次方波变化,就像预期的那样。

在仿真(模拟I/O)作为执行模式下,为了近似再现方波定时,每1秒重复一次方波定时,我需要在时钟滴答场中,从FPGA 40 the的星载时钟参考时钟中输入值1750,如块选项所示。

我不明白这个块,也不明白为什么我不应该在时钟滴答字段,或者简单地说,值1,设置任何接近四千万的除数。基本上,我不知道如何“计时”这些FPGA模拟。

回答 1

Stack Overflow用户

发布于 2017-01-24 09:11:58

桌面执行节点是为基于时间的模拟而设计的,您一定在正确的轨道上。

在顶部设置的是每次调用节点时执行的周期数。在您的例子中,您有1750个滴答,所以每次迭代模拟的时间约为43.75us。

要进行实时模拟,您需要确保执行模拟循环运行所需的模拟时间。在您的例子中,您没有时间在您的模拟循环,所以,为什么1750为您工作是因为这可能是多长时间的循环执行。

如果你在1ms内放一个循环计时器,并把时钟定时器设为40,000 (1ms模拟时间),那么我想你会发现它也能工作。

在某些情况下,执行速度快于实时可能是有益的,因此您只需在数学中说明这一点。例如,如果您将时钟刻度设置为40 (1U模拟时间),那么您可以计数迭代次数并乘以1U来获得实际的时钟时间。

https://stackoverflow.com/questions/41810158

复制相似问题