在NXP LPC1769中设置一个引脚

在NXP LPC1769中设置一个引脚

提问于 2016-11-18 14:45:52

我只需要修改另一个端口/引脚的源代码。我已经尽可能多地和NXP UM10360学习了。

我有那个装置;

"CMSIS_CORE_LPC17xx“中使用的头文件:LPC17xx.h

LPC_PINCON->PINSEL0 |= 0x2<<14; //P0.7 > SCK1

LPC_PINCON->PINSEL0 |= 0x2<<16; //P0.8 > MISO1

LPC_PINCON->PINSEL0 |= 0x2<<18; //P0.9 > MOSI1 和

我想用另一个(从SSP1到SSP0)替换这些引脚。

P0.7 will be P0.15

P0.8 will be P0.17

P0.9 will be P0.18根据手册,我尝试了这个(函数10);

LPC_PINCON->PINSEL0 &= ~((0x3 << 31)|(0x3 << 30));//P0.15, SCK0

LPC_PINCON->PINSEL0 |= ((0x2 << 31)|(0x2 << 30)); //ENable clock

LPC_PINCON->PINSEL1 &= ~((0x2 << 3)|(0x2 << 2));//P0.17, MISO0

LPC_PINCON->PINSEL1 &= ~((0x2 << 5)|(0x2 << 4));//P0.18, MOSI0但是,SPI设备在此之后就停止了。最初的设置上面是很好的工作,并向我展示了良好的SPI信号与逻辑分析仪。但是,有了新的引脚和相应的设置,我只能在Logic上获得CSN和MISO,SCK只启用(没有脉冲)。

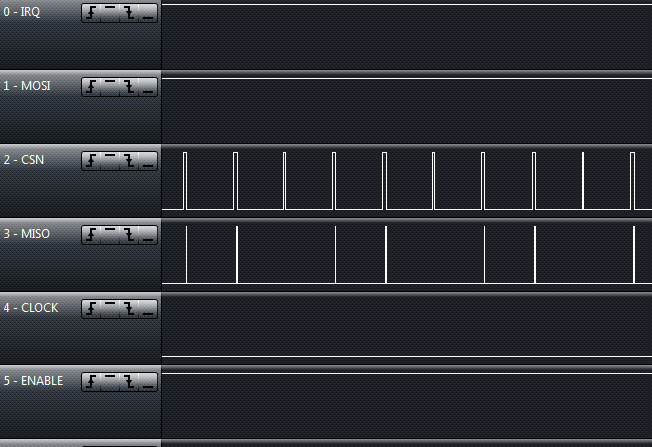

就这样:

我做错了什么?(我对NXP单片机缺乏经验,请容忍我。)

编辑:

为了记录,我终于找到了自己,问题解决了;

LPC_PINCON->PINSEL0 |= 0x2<<30; //SCK0, P0.15

LPC_PINCON->PINSEL1 |= 0x2<<2; //MISO0, P0.17

LPC_PINCON->PINSEL1 |= 0x2<<4; //MOSI0, P0.18

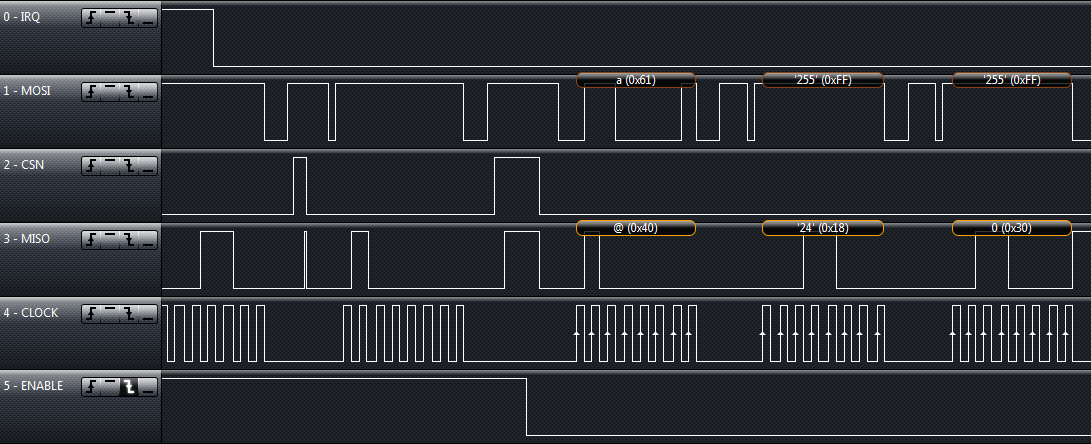

LPC_GPIO0->FIODIR |= (1<<16); //SSEL/CSN, P0.16 这是逻辑分析器的结果;

回答 1

Stack Overflow用户

回答已采纳

发布于 2018-09-11 15:40:38

为了记录,我可以设法建立一个工作的解决方案,只要设置的方式;

LPC_PINCON->PINSEL0 |= 0x2<<30; //SCK0, P0.15

LPC_PINCON->PINSEL1 |= 0x2<<2; //MISO0, P0.17

LPC_PINCON->PINSEL1 |= 0x2<<4; //MOSI0, P0.18

LPC_GPIO0->FIODIR |= (1<<16); //SSEL/CSN, P0.16页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/40679869

复制相关文章

相似问题