系统定时器(可移植逻辑定时器)的设计

系统定时器

计算机包含一个定时器,它包含可编程通道。可编程通道意味着不同持续时间的定时器。如何设计这样一个由四个可编程通道组成的电路,每个通道最初都是禁用的。启用输入、两个通道选择输入和4行持续时间输入可以将任何通道设置为从1-15到15之间的给定持续时间。零意味着禁用通道。四条输出线对应于通道,并在相应的计时器过期时被设置为高。

输入时钟脉冲CP

输入可用IA

频道选择CS0,CS1

持续时间D0…D3

输出

计时器过期: TA,TB,TC,TD

我想使用离散逻辑集成电路,如触发器,逻辑门,解码器,复用器,编码器,etc.Data输入是用按钮(按钮)和输出应该显示在LED上。时钟应该是普通的。

回答 1

Stack Overflow用户

发布于 2016-01-08 16:07:26

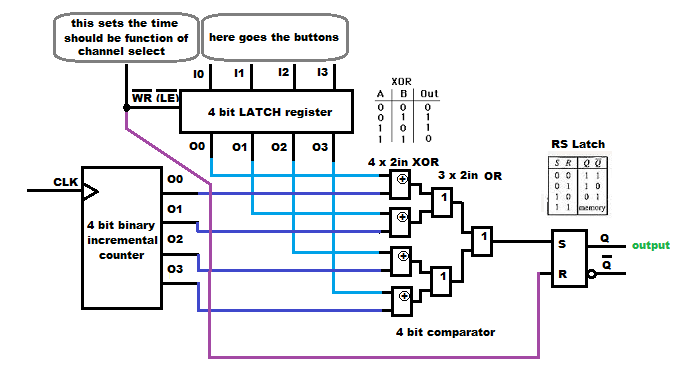

单发计时器由:组成

- n位二进制计数器

由输入时钟源

CP驱动,并由启动输入重新分配。每一个时钟脉冲都会增加它的值。复位输入应连接到计时器启动信号。 - n位锁存寄存器

存储计时器间隔值(每个信道持续时间

D0..D3) - n位比较器

若要比较计数值和间隔值,请执行以下操作。等位的XOR是零,所以如果您或所有and位在一起,如果锁存寄存器值和计数器值都相同,则结果是

0。 - 输出触发器

为了记住计时器的过期(对于非脉冲模式的操作),输出是您的

TA.TB,TC,TD,启动脉冲也应该在电路上重新设置RS,我通过WR来做这件事,但是我怀疑您会有单独的启动信号。

就像这样:

您需要考虑使用的集成电路的否定和辅助输入,以使它正常工作(一些已经否定WR,有些没有.对于所有的引脚也是如此,所以总是检查数据表)。因此,不要忘记添加芯片选择和输出启用信号到他们的工作条件。

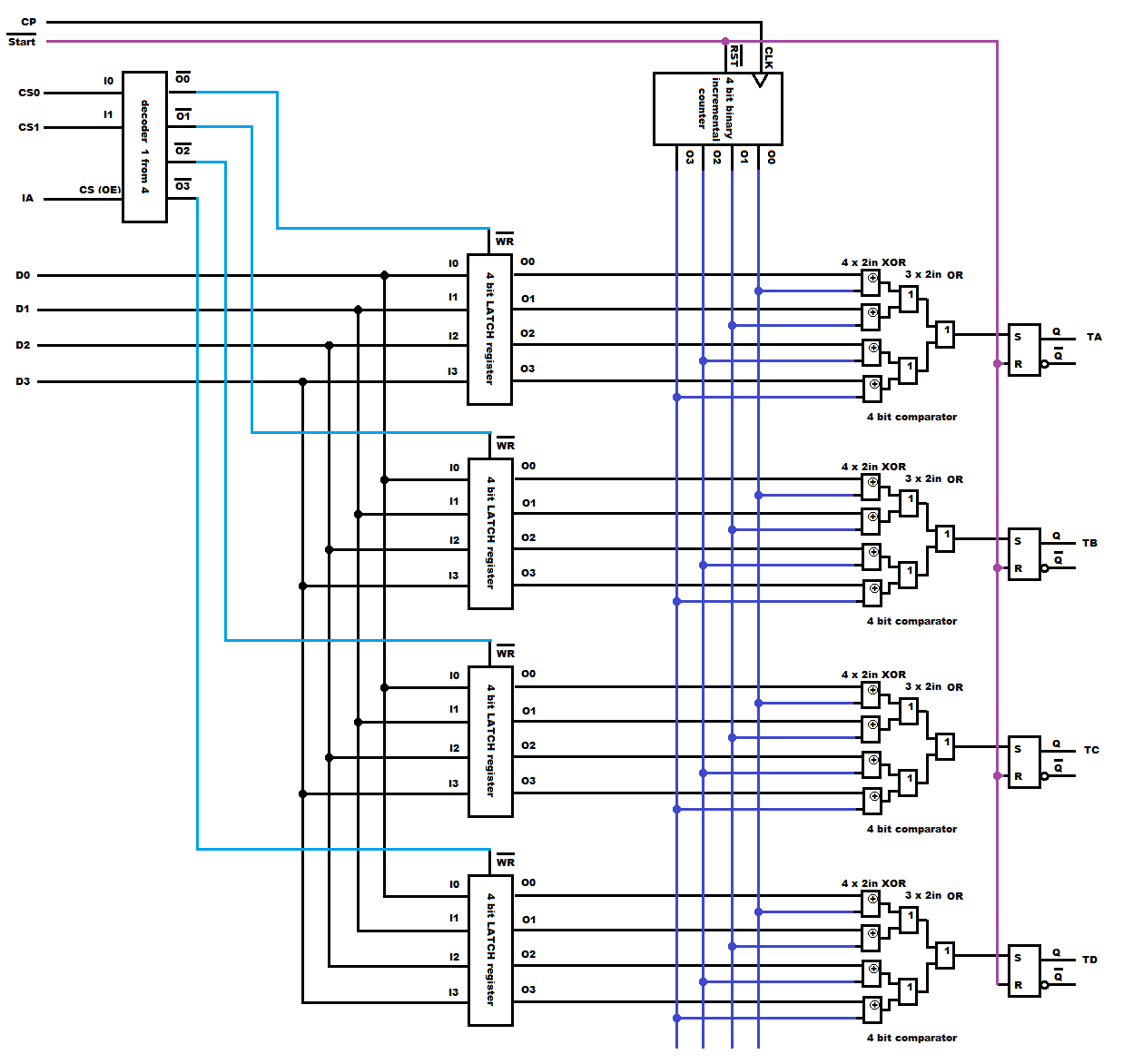

多通道定时器

您只需为每个通道添加锁存器、和比较器,每个通道都连接到同一个计数器。棘手的部分是渠道的选择和启动部分。您需要添加解码器1 from 4来选择正确的锁存,同时设置D0..D3。为了画出这部分的电路,我需要更多地了解这部分的目的.另外,如果您只手动设置间隔,那么您可以使用DIP开关,而不是锁存器、和选择电路,这使它更加简单。

所有这些都可以由NAND或NAND网关来实现,而不是具体的IC实现。为此,您需要使用Karnaugh Maps和布尔代数。

有一段时间我用原始的门做了一些事情,因为现在使用单片机/FPGA更容易、更便宜、更快,所以请注意,我可能错过了一些琐碎的东西(比如否定门).无论如何,即使这样,这也应该是计时器背后的想法。

BTW C++表示是:

int cnt=0,D=?;

bool TA=0;

for (;;)

{

if (cnt==D) TA=1;

cnt=(cnt+1)&15;

}Edit1 4通道版本

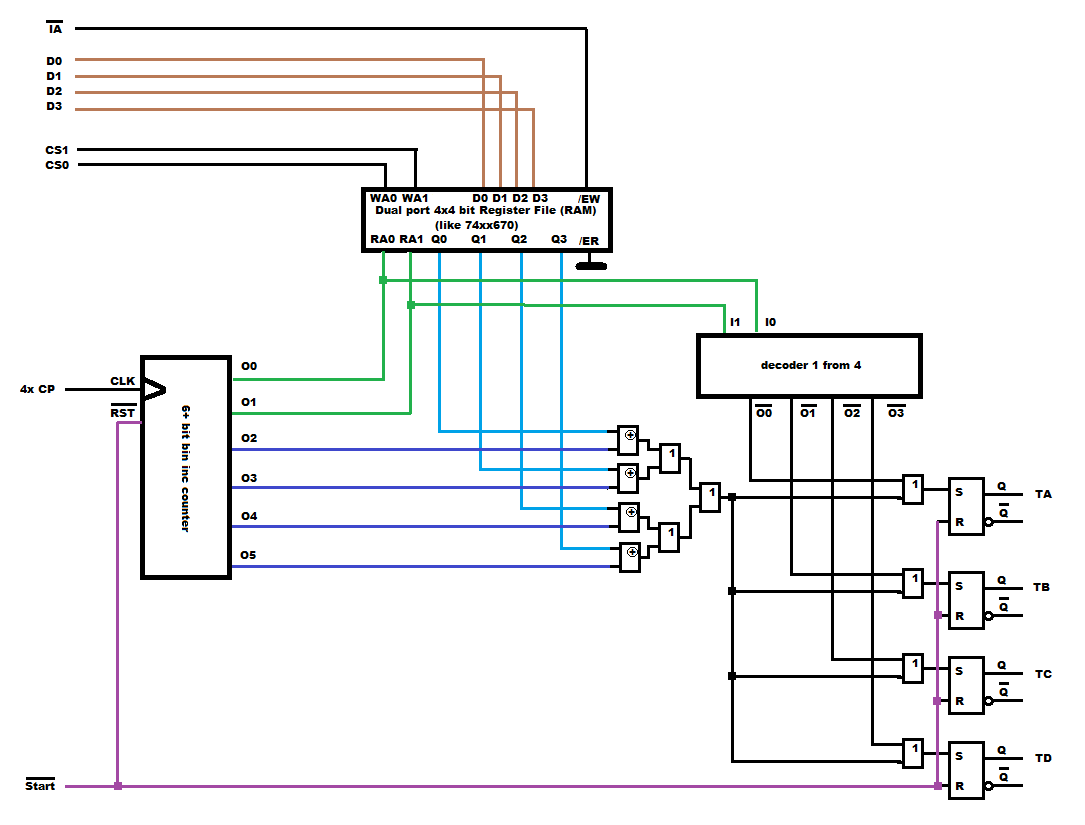

这是基于上述案文。还有另一种选择,使用较少的组件,使用4 nibble模块,而不是锁存寄存器和单定时器的解码器组成,通过所有信道连续循环4倍CP乘时钟(例如,通过XORing延迟CP信号)。

https://stackoverflow.com/questions/34679211

复制相似问题