带cocotb的verilog : assign语句

带cocotb的verilog : assign语句

提问于 2015-11-08 17:05:41

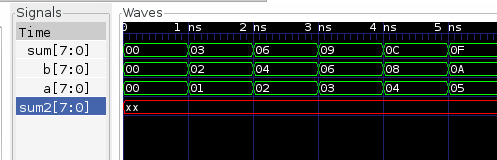

我的verilog代码是一个只使用assign sum = a+b的加法器。问题是,在使用cocotb运行它时,sum仍然是未知的,尽管a和b有有效值。当我使sum成为reg类型时,它就能工作。

`timescale 1 ns / 1 ps

module adder(input [7:0] a,

input [7:0] b,

output reg [7:0] sum,

output [7:0] sum2);

assign sum2=a+b; //Trouble is here

always@(a,b) begin

sum=a+b; //This works

end

`ifdef COCOTB_SIM

initial begin

$dumpfile("adder.vcd");

$dumpvars();

end

`endif

endmodule

回答 1

Stack Overflow用户

回答已采纳

发布于 2015-11-08 17:28:59

我相信这实际上是由在0.9.7版本中出现的Icarus中的一个bug引起的。

如果您升级到最新的开发版本,您会发现一个持续的分配很好。其他模拟器也处理连续分配罚款。

如果您被困在Icarus的那个版本上,您可以通过将任务放在一个过程中来解决它,就像您发现的那样。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/33596587

复制相关文章

相似问题