结构Verilog 8-函数ALU

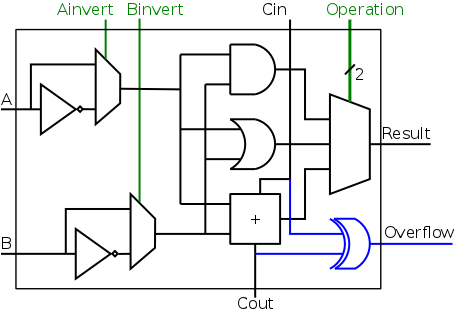

我知道如何使用行为风格编写ALU,但我完全不知道如何使用结构设计来编写ALU。我需要一个8功能的位片结构ALU,这样我就可以通过一个传递的参数来改变字的大小,并且它仍然可以工作。我找到了一个2功能ALU的原理图,但是有人能告诉我如何将它转换成8函数,或者可能将我链接到Verilog示例吗?这是两个功能的ALU原理图:

我对真值表、k-映射等还记不起,甚至连我自己也想不出这方面的逻辑。不知道该从哪里开始。任何帮助都是非常感谢的,谢谢!

回答 1

Stack Overflow用户

发布于 2015-10-10 13:03:19

除非您试图将逻辑简化为最小形式(这确实是浪费精力,因为合成工具本身非常擅长这样做,至少在合并术语以获得更小的功能等价逻辑时是如此),否则您可以进一步解决这个问题。在编写行为Verilog时,您通常应该这样想,因为这样做使您的设计更有可能将其合成成一个可行的、可靠的netlist。

您有一个原理图,所以先从设计的主要部分开始,并实现模块来完成这些功能。例如,设计中有许多2x1 muxes。因此,我们应该实现从正确的输入中选择的逻辑。什么是穆克斯?这是一个基本的组合函数,如下所示:

S A B O

----------

0 0 x 0

0 1 x 1

1 x 0 0

1 x 1 1如果S是0,O = A,S是1,O = B。因此,我们可以将它们重新格式化为逻辑表达式:O = ~S & A | S & B (注意,如果S = 0,我们将传递A,B项将为0‘Note,如果S为1,则反之亦然)。

现在,只需在Verilog门的原语中实现这一点:

module mux2x1(input A,

input B,

input S,

output O);

wire AO, BO, NOT_S;

not n1(NOT_S, S); // NOT_S = ~S;

and a1(AO, A, NOT_S), // AO = A & ~S;

a2(BO, B, S); // BO = B & S;

or o1(O, BO, AO); // O = (A & ~S) | (B & S);

endmodule现在,为了增加A、B和O的宽度,我们只需要为A、B和O的每一位做一串这样的muxes。我们可以这样做,但可以生成大量的mux模块,或者对模块中的逻辑进行如下操作:

module mux2x1 #(parameter W = 1)

(input [W-1:0] A,

input [W-1:0] B,

input S,

output [W-1:0] O);

wire [W-1:0] AO, BO;

wire NOT_S;

genvar i;

not n1(NOT_S, S); // NOT_S = ~S;

generate begin

for (i = 0; i < W; i = i + 1) begin : mux_w

and a1(AO[i], A[i], NOT_S), // AO[i] = A[i] & ~S;

a2(BO[i], B[i], S); // BO[i] = B[i] & S;

or o1(O[i], BO[i], AO[i]); // O[i] = (A[i] & ~S) | (B[i] & S);

end

end

endmodule现在,您已经看到了一个有效的示例,我希望您可以以同样的方式完成其他模块(比如加法器和4x1mux)。这并不是一种正式的方式,但它有助于简单地考虑事情。另外,如果你在逻辑上有困难的话,在线上会有很多加法器结构。

https://stackoverflow.com/questions/33047934

复制相似问题