点阵iCE40 40-HX8K板- UART

点阵iCE40 40-HX8K板- UART

提问于 2015-09-04 20:58:43

我的格子iCE40-HX8K板有以下verilog代码:

uart.v:

module uart(input clk, output TXD);

reg [3:0] count;

reg [9:0] data;

reg z;

initial begin

data[9:0] = 10'b1000000000; // Startbit = 1, Stopbit = 0

z = 0;

end

always@(posedge clk)

begin

if(count == 1250) //9600x per Second (1250) = Baudrate

begin

count <= 0;

TXD = data[z];

z = z + 1;

if(z == 10)

begin

z = 0;

end

else

begin

end

end

else

begin

count <= count + 1;

end

end

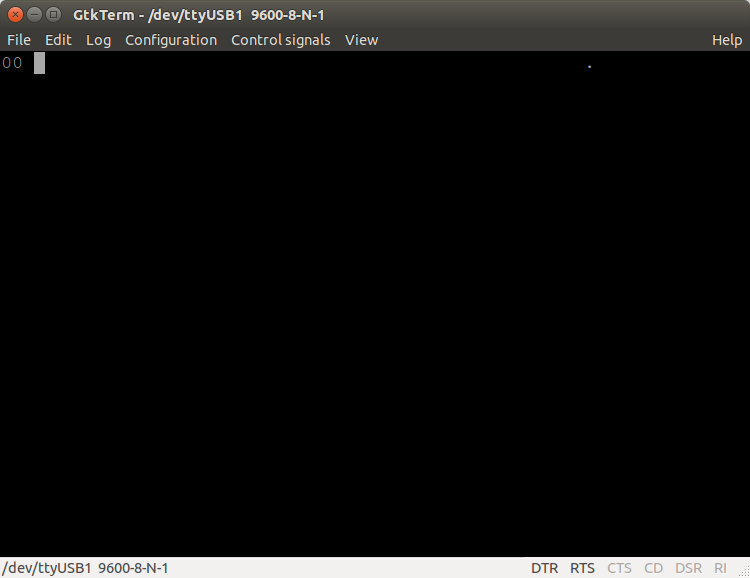

endmodule对于接收UART-数据,我使用Ubuntu14.04下的gtkterm。我已将gtkterm中的波德率设置为9600。如果我现在用我每编程一次所收到的代码对我的FPGA编程,就会得到一个十六进制"00“(不管8个使用位)。

有人能给我个提示吗?

谢谢您一直鼓励我。

回答 1

Stack Overflow用户

回答已采纳

发布于 2015-09-05 09:30:48

您的设计至少有两个明显的问题:

- 您的

count只有4位宽,因此不能计算到1250。它必须至少有11位宽才能计数到1250。 - 而且你的

z只有1位宽,所以它只能容纳0和1。它必须至少有4位宽才能计数到10。

您还应该阅读阻塞与非阻塞分配。在顺序逻辑中使用阻塞分配的方式可能会导致verilog仿真模型中的争用条件。

您应该始终为您的HDL代码编写测试工作台,并在尝试在硬件中运行它之前对其进行模拟。为您的设计搭建一个测试平台将非常容易:

module uart_testbench;

reg clk = 1;

always #5 clk = ~clk;

uart uut (

.clk(clk)

);

initial begin

$dumpfile("uart.vcd");

$dumpvars(0, uut);

repeat (1000000) @(posedge clk);

$finish;

end

endmodule页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/32406503

复制相关文章

相似问题