使用逻辑门的加密/解密器(XOR,NEG/NOT,NAND)

我正在研究Verilog中的一个项目,该项目将加密20位数字并使用XOR、NOT和NAND门将其解密。

为了加密,

- 输入

XORxorEncDec(异或的预定义操作数) NOT输入(也是1的comp)- 输入

NANDnandEncDec(NAND的预定义操作数)

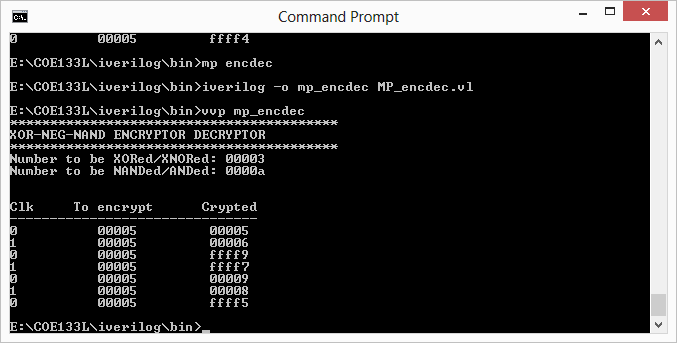

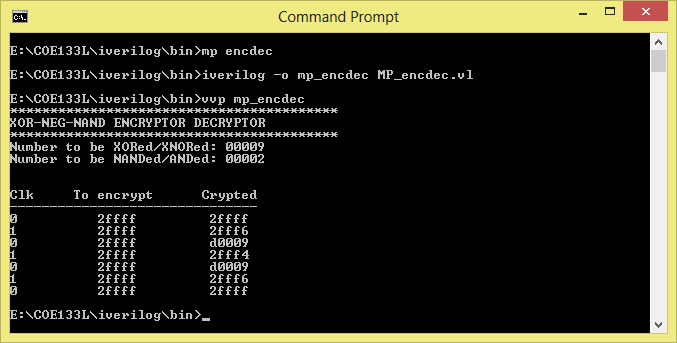

我的解密器有问题。数字是十六进制的。下面是我的程序的一个示例输出:

我现在的解密逻辑(这是错误的)是

- 输入

NAND2的nandEncDec的comp NOT2输入法- 输入

XOR2的xorEncDec的comp

我觉得我已经接近答案了,因为每个解密阶段的输出似乎都是负值。你能帮我修复我的解密算法吗?我并不是真的在寻找Verilog代码中的答案,即使是算法或正确的门也可以。

回答 3

Stack Overflow用户

发布于 2014-12-11 18:31:28

NAND是一种可灌溉的操作:

a b (a NAND b)

0 0 1

0 1 1

1 0 1

1 1 0如果b为0,并且您知道(a NAND b)的结果为1,则无法知道a是0还是1。因此,您的加密算法存在缺陷,无法解密其输出。

(你大概知道以下几点,但我还是觉得不得不这么说:制作自己的密码算法是一项有趣的练习,但永远不要用自己的密码来做任何严肃的事情;它会被打破。这适用于每个人,除了专业的密码学家,甚至他们必须提交他们的算法进行彻底的公开审查,然后任何人都会梦想使用它们。)

Stack Overflow用户

发布于 2014-12-11 18:31:42

我想你有麻烦了,因为没有额外的侧信息是不可能倒置NAND门的。

问题是1 ~& 0与0 ~& 0是相同的,因此无法区分输入0和输入1。

Stack Overflow用户

发布于 2015-01-11 03:39:09

我已经找到了一种方法来解密不可逆的操作,比如NAND,在NAND加密之后生成线索的条件。当然,我认为,这并不是因为它违反了加密的功能--安全性。

总之,先有背景。由于输入0 & 0和1 & 0,NAND是可逆的操作。两种方法都会在输入NAND之后输出1。一旦你‘解密’它,给定1 & 0,就无法判断上一个加密比特是0还是1.除非您在NAND加密之后生成一个标记。

为了实现这个标记,我使用了两个数组-- 0 & 0的数组A和1 & 0的数组B。数组被实例化为完全0(或者1's,如果您愿意)。例如,如果每个输入的第4位是0 & 0,数组A的第4位将被设置为1 (或者0,如果您将其设置为所有1的)。

然后使用标记数组进行解密。

这是我的程序的一个证明,以显示算法的工作。

https://stackoverflow.com/questions/27429465

复制相似问题