全局内存负载/存储效率与全局内存一致性

我有以下简单代码:

#include<stdio.h>

#define BLOCKSIZE_X 32

#define BLOCKSIZE_Y 1

int iDivUp(int a, int b) { return ((a % b) != 0) ? (a / b + 1) : (a / b); }

#define gpuErrchk(ans) { gpuAssert((ans), __FILE__, __LINE__); }

inline void gpuAssert(cudaError_t code, char *file, int line, bool abort=true)

{

if (code != cudaSuccess)

{

fprintf(stderr,"GPUassert: %s %s %d\n", cudaGetErrorString(code), file, line);

if (abort) exit(code);

}

}

__global__ void kernel0(float *d_a, float *d_b, const unsigned int M, const unsigned int N)

{

const int tidx = threadIdx.x + blockIdx.x * blockDim.x;

const int tidy = threadIdx.y + blockIdx.y * blockDim.y;

if ((tidx < M)&&(tidy < N)) {

d_b[tidy * M + tidx] = d_a[tidy * M + tidx];

}

}

void main()

{

const unsigned int M = 32;

const unsigned int N = 1;

float *d_a; cudaMalloc((void**)&d_a, M*N*sizeof(float));

float *d_b; cudaMalloc((void**)&d_b, M*N*sizeof(float));

dim3 dimGrid(iDivUp(M, BLOCKSIZE_X), iDivUp(N, BLOCKSIZE_Y));

dim3 dimBlock(BLOCKSIZE_X, BLOCKSIZE_Y);

kernel0<<<dimGrid, dimBlock>>>(d_a, d_b, M, N);

gpuErrchk(cudaPeekAtLastError());

gpuErrchk(cudaDeviceSynchronize());

cudaDeviceReset();

}它执行两个32 float数组之间的赋值,我试图理解全局内存合并访问与全局内存负载/存储效率以及其他度量/事件之间的关系。

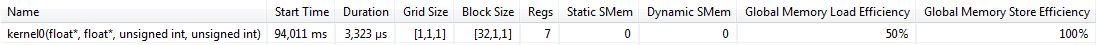

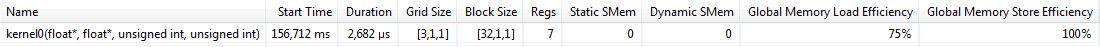

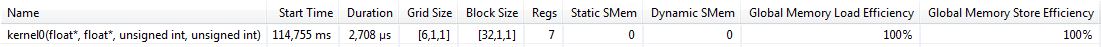

Visual显示了以下指标:

Global Memory Load Efficiency = 50%

Global Memory Store Efficiency = 100%全局内存负载效率的价值让我感到惊讶。在这两种情况下,我都会期望100%的效率,因为我相信我正在执行一种完美的合并内存访问。所以我的问题是:

当我执行合并的内存访问时,为什么我有50%的全局内存加载效率,而我却拥有100%的全局内存存储效率?

我还调查了其他指标/事件,这些指标/事件可能值得报告:

gld_inst_32bit = 32 (Number of 32-bit global memory load transactions)

gst_inst_32bit = 32 (Number of 32-bit global memory store transactions)实际上,我请求加载/编写32 floats。

uncached global load transaction = 0 (Number of uncached global load transactions)

l1 global load miss = 2 (Number of global load misses in L1 cache)根据我(可能是错误的)理解,上述两件事似乎是矛盾的。在l1缓存丢失的情况下,我希望第一个事件与0不同。

gld_request = 1 (Number of executed global load instructions per warp in a SM)

gst_request = 1 (Number of executed global store instructions per warp in a SM)这似乎与我正在执行完全合并的内存访问这一事实相一致。

拆卸代码如下:

/*0000*/ MOV R1, c[0x1][0x100]; /* 0x2800440400005de4 */

/*0008*/ S2R R3, SR_CTAID.Y; /* 0x2c0000009800dc04 */

/*0010*/ S2R R4, SR_TID.Y; /* 0x2c00000088011c04 */

/*0018*/ IMAD R4, R3, c[0x0][0xc], R4; /* 0x2008400030311ca3 */

/*0020*/ S2R R0, SR_CTAID.X; /* 0x2c00000094001c04 */

/*0028*/ ISETP.LT.U32.AND P0, PT, R4, c[0x0][0x2c], PT; /* 0x188e4000b041dc03 */

/*0030*/ S2R R2, SR_TID.X; /* 0x2c00000084009c04 */

/*0038*/ IMAD R0, R0, c[0x0][0x8], R2; /* 0x2004400020001ca3 */

/*0040*/ ISETP.LT.U32.AND P0, PT, R0, c[0x0][0x28], P0; /* 0x18804000a001dc03 */

/*0048*/ @!P0 BRA.U 0x78; /* 0x40000000a000a1e7 */

/*0050*/ @P0 IMAD R2, R4, c[0x0][0x28], R0; /* 0x20004000a04080a3 */

/*0058*/ @P0 ISCADD R0, R2, c[0x0][0x20], 0x2; /* 0x4000400080200043 */

/*0060*/ @P0 ISCADD R2, R2, c[0x0][0x24], 0x2; /* 0x4000400090208043 */

/*0068*/ @P0 LD R0, [R0]; /* 0x8000000000000085 */

/*0070*/ @P0 ST [R2], R0; /* 0x9000000000200085 */

/*0078*/ EXIT; /* 0x8000000000001de7 */编辑

我的配置: CUDA 6.5,GeForce GT540M,Windows 7。

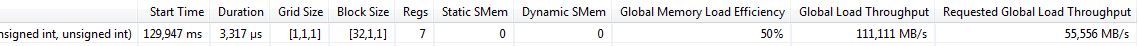

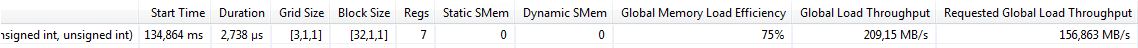

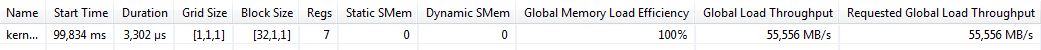

如果我将M从32增加到64,启动两个块,并使我的卡的两个可用流多处理器繁忙,那么全局内存负载效率将转向100%,这些是新的度量/事件:

gld_inst_32bit = 64

gst_inst_32bit = 64

uncached global load transaction = 0

l1 global load miss = 2

gld_request = 2

gst_request = 2gld_inst_32bit、gst_inst_32bit、gld_request和gst_request的增长是预期的,而且是一致的,因为现在我是loading7storing 64 float和2全局内存负载/存储合并请求。但是,我仍然不明白uncached global load transaction和l1 global load miss如何保持不变,而全局内存负载吞吐量的变化是为了提供100%效率。

编辑

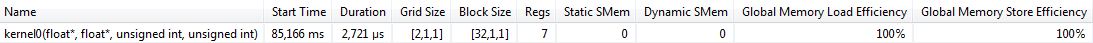

开普勒K20c在M=32上的结果

Global Memory Load Efficiency = 100%

Global Memory Store Efficiency = 100%

gld_inst_32bit = 64

gst_inst_32bit = 64

gld_request = 1

gst_request = 1

uncached global load transaction = 1

l1 global load miss = 0

l1 global load hit = 0现在,Visual报告一个未被缓存的全局负载事务,但没有l1全局负载丢失。

编辑

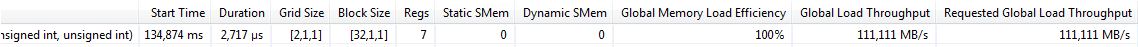

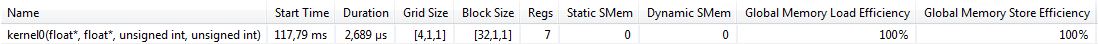

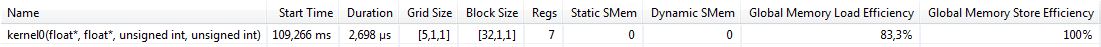

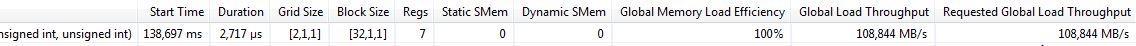

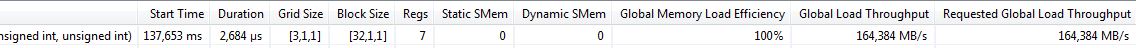

我已经对这个问题做了更多的研究,增加了M的价值,并保持了BLOCKSIZE_X的固定。

当块数为奇数时,即我的GT540M卡的两个流多处理器的负载不平衡,则全局内存负载效率低于100%,否则为偶数情况下的100%。在奇数情况下,只要增加块数,全局内存负载效率就会缓慢地趋向于100%。

如果按照@Jez的建议,通过使用L1编译禁用-Xptxas -dlcm=cg缓存,那么全局内存负载效率总是等于100%,因为它是全局内存存储效率。我知道全局内存存储不使用L1缓存,而只使用L2。

一些图片显示,对于不同的M值,全局内存负载效率的行为

M=32

M=64

M=96

M=128

M=160

M=192

请注意,M是32的整数倍数,可以通过一次翘曲加载整个缓存行。

通过禁用L1,我拥有:

M=32

M=64

M=96

编辑-特斯拉C2050的结果

M = 32 33.3%

M = 64 28.6%

M = 96 42.9%

M = 128 57.1%

M = 160 71.4%

M = 192 85.7%

M = 224 100%

M = 256 114%

M = 288 90%同样,如果禁用L1缓存,则在所有情况下都具有100%全局内存加载效率。

回答 1

Stack Overflow用户

发布于 2014-09-25 14:54:23

计数器的精度

NVIDIA分析器可以收集原始计数器和度量。许多度量标准要求内核执行多次。理想情况下,分析器能够在一次传递中收集度量的所有原始计数器,但考虑到性能监视系统的局限性,这是不可能的。

在费米结构上,用于收集全球内存负载效率和全局存储效率的L1统计数据的HWPM系统只能观察到每台GPC一个L1单元。对于GF100 (C2050),这相当于25%的观察。

如果工作负载没有完全填满机器,并且每个单元的工作量是相同的,分析器将无法提供准确的结果。

在开普勒结构上,HWPM系统可以从每个L1上收集L1的统计数据,但对于L2仍然有一定的局限性,造成的误差很小。

在Maxwell体系结构上,内存系统与全局、局部和表面请求有很大的不同,它们现在都经过统一的L1/TEX缓存。

缓存的VS.UNCACHED

在费米体系结构中,所有全局负载/存储都是通过L1缓存实现的。未缓存的全局负载/存储仍然通过L1,使用LSU事务,并需要标记查找来使缓存行失效。Atomics是通过L1进行全局访问的唯一形式,不会使L1缓存失效。

开普勒结构有一些小的变化。默认情况下,大多数芯片不缓存全局内存访问,因此所有全局负载都是未缓存的。在GK110和GK208芯片上,可以使用新的LDG指令通过TEX缓存加载全局数据。

从SM到L1的缓存和非缓存的全局负载事务是128个字节。

缓存的全局负载事务(从L1到L2 )作为4个32B请求完成。

从L1到L2的未缓存的全局负载事务是作为最小数量的32B请求完成的。

https://stackoverflow.com/questions/25983544

复制相似问题