如何推导出全1位加法器电路设计的异或变体?

如何推导出全1位加法器电路设计的异或变体?

提问于 2014-02-20 11:59:30

我试图找出如何在一个完整加法器中找到求和的简短版本,从真值表中我得到了这个DNF:

(A && ~B && ~C) || (~A && B && ~C) || (~A && ~B && C) || (A && B && C)

其中A = A,B = B和C = CIn

但根据维基百科的说法,这相当于:

A XOR B XOR C

有什么方法可以让我找到后一个版本,还是只需要在真值表中“看到”?

谢谢!

回答 1

Stack Overflow用户

回答已采纳

发布于 2014-02-23 00:03:43

DNF中的术语有一个共同点:输入的奇数数是真的。

如果一个全加法器的输入行中有一个奇数(一个或三个)是1,则它的输出行是1。如果零输入为1 (= all为0),则输出为0。如果两个输入为1,则执行为1,但输出保持为0.

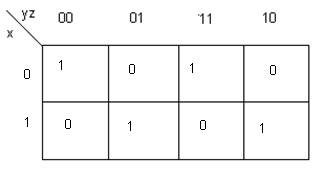

当您将您的真值表转换为一个卡诺图时,您将得到XORs典型的棋盘模式。最后,你是对的:事实上,“看到它”确实有帮助。

(从这里复制的卡诺地图图像)

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/21907154

复制相关文章

相似问题