为什么需要内存对齐?

我在网上读了一些关于内存对齐的文章,可以理解从正确对齐的内存(取2字节对齐)我们可以一次快速地获取数据。

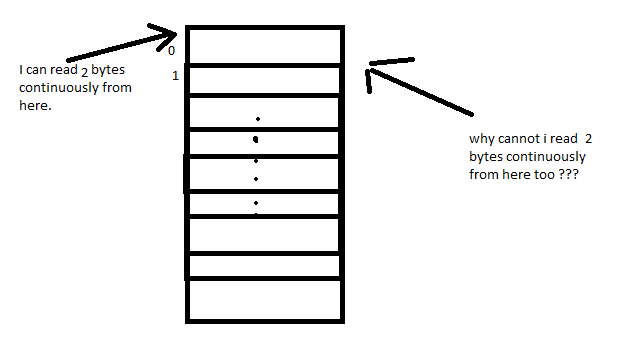

但是如果我们有内存,就像一个单一的硬件块,那么给定一个地址,为什么我们不能直接从那个位置读取2字节。像这样:

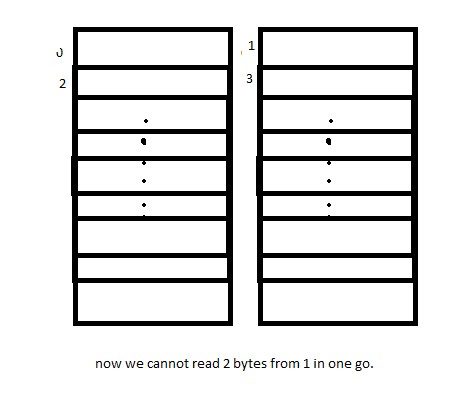

我想过了。我认为,如果记忆是在奇偶银行,那么这个理论就适用了。

我错过了什么?

回答 3

Stack Overflow用户

发布于 2012-10-14 10:22:40

您的图片描述了我们(人类)如何可视化计算机内存。

在现实中,把内存看作是巨大的比特矩阵。每个矩阵列都有一个“读取器”,可以从该列读取/写入任何位。每个矩阵行都有一个“选择器”,它可以选择读取器将要读/写的特定位。

因此,此读取器可以同时读取整个选定的矩阵行。此行的长度(矩阵列数)定义了一次读取数据的数量。例如,如果您有64列,您的内存控制器可以一次读取8个字节(不过,它通常可以读取更多字节)。

只要您保持数据对齐,您将需要较少的这些内存访问。即使您只需要读取两位,但它们位于不同的行,您也需要对内存进行两次访问,而不是一次。

此外,写作还有一个完整的方面,这是一个不同的问题。

正如您可以读取整行一样,您也可以编写整行。如果您的数据没有对齐,那么当您编写不是整行的内容时,您将需要进行读-修改-写入(读取该行的旧内容、修改相关部分和编写新内容)。

Stack Overflow用户

发布于 2012-10-14 11:14:58

来自内存的数据通常在一组与总线宽度匹配的线路上传递给处理器。例如,如果总线宽为32位,则从总线到处理器有32条数据线(以及用于控制信号的其他线路)。

在处理器内部,各种电线和开关将这些数据传递到任何需要的地方。如果您将32位对齐位读入寄存器,连线可以非常直接地将数据传递到寄存器(或其他保存位置)。

如果将8或16对齐位读入寄存器,则连线可以以相同的方式传递数据,而寄存器中的其他位被设置为零。

如果将8或16位未对齐位读入寄存器,则连线无法直接传递数据。相反,比特必须被移动:它们必须通过一组不同的电线,这样它们才能被“移动”,以便与进入寄存器的连线保持一致。

在一些处理器中,设计人员增加了电线和开关来实现这种移动。就硅的含量而言,这可能是非常昂贵的。您需要大量额外的电线和开关,以便能够将任何可能的未对齐字节移动到所需的位置。因为这太贵了,在一些处理器中,没有一个完整的移位器可以立即完成所有的移位。相反,移位器可能只能在每个CPU周期中移动一个字节左右的位,并且需要几个周期才能移动几个字节。在一些处理器中,根本没有连接,所以所有的负载和存储必须对齐。

Stack Overflow用户

发布于 2012-10-14 10:14:20

在第一种情况下(单个硬件),如果需要读取2个字节,那么处理器就必须发出两个读周期,这是因为内存是字节寻址的,即每个字节都提供一个唯一的地址。

将内存组织为银行可以帮助CPU在单个读取周期内将更多的数据提取到寄存器中。这种技术有助于减少读取周期--与CPU的处理能力相比,这是一个非常缓慢的过程。因此,对于单个读取周期,您可以读取更多的数据。

https://stackoverflow.com/questions/12881179

复制相似问题