是否有一些实例来说明数据路径和控制中的流水线?

数据路径中的流水线只是简单地分配/切割(理论上)资源。但流水线控制意味着每个资源在管道阶段得到独立的控制信号?

例如,在大多数RISC体系结构中,我们有5个阶段的流水线,而Mem管道阶段有单独的加载或存储控制信号?

有一些控制流水线的实际例子吗?

回答 2

Stack Overflow用户

发布于 2021-12-01 15:59:53

在经典的5级管道中,管道的每一阶段都有来自前一阶段的输入(当然,第一阶段除外),而管道的每一阶段都有到下一阶段的输出(当然,最后一阶段除外),这是合理的,这些输入和输出是由数据和控制信号组成的。

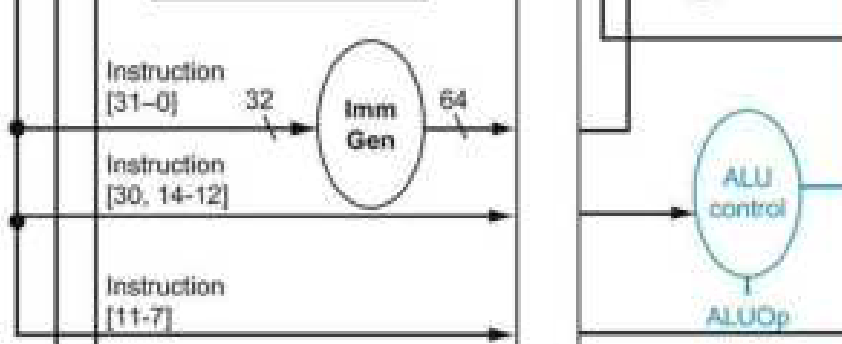

EX阶段需要知道要执行什么ALU操作(control: ALUOp)和ALU输入操作数(数据)。

MEM阶段需要知道是读取内存(control: MemRead)还是写内存(control: MemWrite) (加上扩展的大小和类型,通常是模糊的),以及在哪里读取(数据:地址)和写入什么(数据:写入数据)。

WB阶段需要知道是否要写寄存器(控制: RegWrite)和要写什么寄存器(数据:写寄存器),以及要写入寄存器的值(数据:写数据)。

在单级处理器中,所有这些控制信号都是通过ID阶段的查找(使用操作码)生成的。当处理器被流水线化时,这些信号要么从一个阶段转发到另一个阶段,要么每个阶段都必须使用opcode重复查找(然后,操作码需要从一个阶段转发到另一个阶段,以便每个阶段重复查找,尽管可能是为了例外情况). (我相信,与转发控制信号相比,在每个阶段重复查找将带来成本(时间和硬件),特别是对于WB,它应该在一个周期的前半部分执行。)

由于WB阶段需要知道是否写入寄存器,必须将该信息(控制: RegWrite)从MEM阶段传递给它,后者从EX阶段获得它,从ID阶段获得它,在该阶段它是通过查找操作码生成的,EX & MEM不使用RegWrite控制信号,但必须接受它作为输入,以便将其作为输出传递到下一阶段。

对于MEM所需的控制信号也是如此: MemRead和MemWrite是在ID中生成的,它们从EX传递到MEM (不在EX中使用),而MEM不需要进一步传递这些信号,因为WB也不使用这些信号。

Stack Overflow用户

发布于 2021-12-01 17:03:01

如果你看一看“计算机组织与设计”第四章RISC-V版(第一版图4.44 ),它显示了从一个阶段输出的控制信号经过阶段流水线寄存器,然后进入下一个中间阶段。例如,指令30,14-12被输入ID/EX,然后在EX阶段由ALU Control读取。这是一个流水线控制信号的例子。

https://stackoverflow.com/questions/70184065

复制相似问题