具有同步复位的边缘触发T触发器的Verilog结构描述(R)

具有同步复位的边缘触发T触发器的Verilog结构描述(R)

提问于 2020-07-06 11:34:15

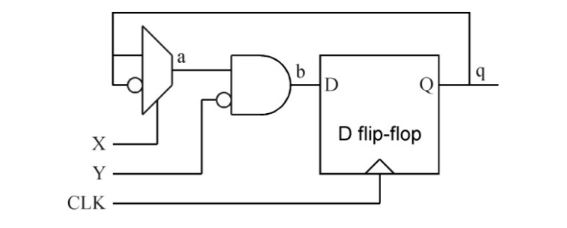

我试图连接一个Verilog结构描述的边缘触发T触发器与同步复位(R)。这是这个元件的电路:

现在假设我已经为这个原理图中的每个块编写了行为描述,下面是我对这个电路的结构描述,通过实例化电路中的每一个块:

module edge_trig_flipflop_structure (

input x,y,clk,

output q,

wire a,b,c,d

);

inv u1(c,q);

mux_2x1 u2 (q,c,x,a);

inv u3(d,y);

and_2_1 u4(b,a,d);

d_flipflop u5(b,clk,q);

endmodule这是这个电路的有效代码吗?换句话说,我真的需要用于逆变器的两条额外的电线,即电线c和d,还是有另一种有效的方法来编写这段代码?

编辑:下面是每个组件的代码,用于了解每个组件声明中端口的顺序。

module mux_2x1 (

input a,

input b,

input sel,

output reg c

);

always @ (*) begin

case ( sel)

1'b0: c=a;

1'b1: c=b;

default : $dispaly ("error");

endcase

end

endmodule

module d_flipflop ( input d,clk , output reg q);

always @ (posedge clk ) begin

q=d;

end

endmodule

module inv(output reg b, input a);

always @ (a) begin

b=~a;

end

endmodule

module and_2_1 ( output reg c,input a,b);

always @(a or b) begin

if (a==1'b1 & b==1'b1)

c= 1'b1;

else

c=1'b0;

end

endmodule回答 1

Stack Overflow用户

回答已采纳

发布于 2020-07-06 12:12:26

默认情况下,Verilog不要求您声明所有信号。如果信号出现在端口连接中,它们将隐式为1位wire类型.

但是,正如您所做的那样,使用wire显式声明所有信号是很好的做法。

还可以更改默认行为,并使用此编译器指令要求显式声明信号:

`default_nettype none因为您也关心连接,所以按名称而不是按位置建立连接是一种很好的做法。它更详细,但它将有助于避免简单的连接错误。例如:

inv u1 (.b(c), .a(q));您的模块头上有编译错误。您可能打算用这种方式编写代码:

module edge_trig_flipflop_structure (

input x,y,clk,

output q

);

wire a,b,c,d;页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/62755192

复制相关文章

相似问题