Verilog

Verilog

提问于 2021-05-06 19:12:20

我正在研究这个Verilog文件:

`default_nettype none

module stroboscope(i_clk, o_led);

input wire i_clk;

output wire o_led;

reg [19:0] counter;

initial counter = 0;

always @(posedge i_clk)

begin

counter <= counter + 1'b1;

end

assign o_led = &counter[19:15];

endmodule我已经知道,如果我将assign从当前状态改为显示,闪烁o_led的频率保持不变,而它的占空比增加到100% (当它打开时)。

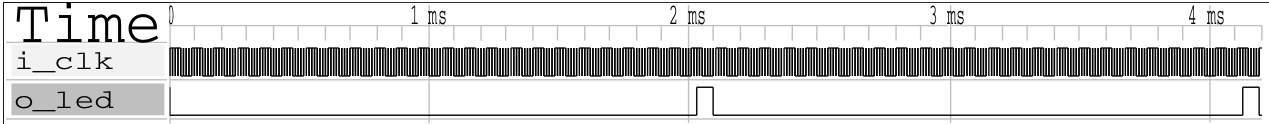

assign o_led = &counter[19:19];

现在可以减少占空比,办法是将同一行改为:

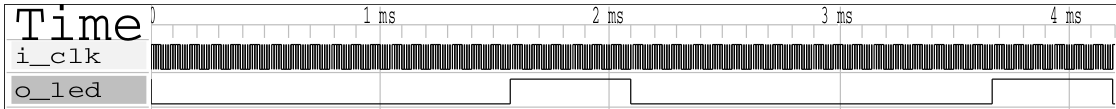

assign o_led = &counter[19:17];

再一次..。通过将同一行设置为:

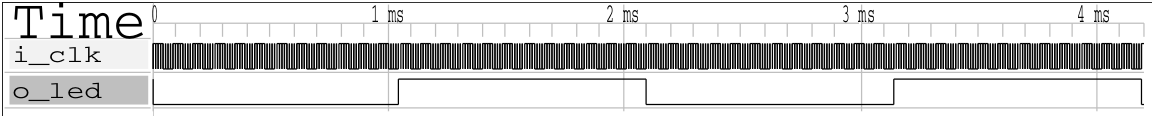

assign o_led = &counter[19:15];

最后,如下图所示,设置相同的标准将使关税周期为0%:

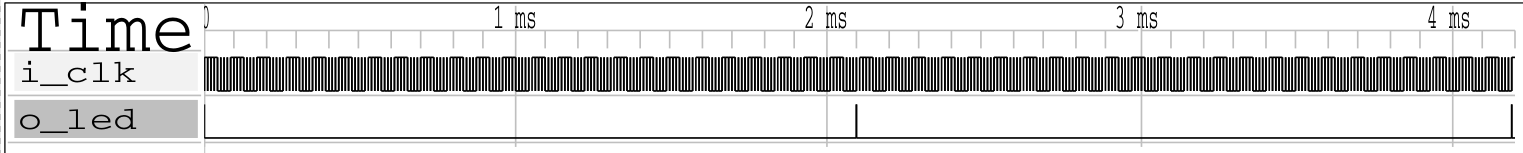

assign o_led = &counter[19:0];

那么,在这种情况下,表示“和约简”的一元&操作符是如何实现这一点的呢?

我知道一个简单的例子,它是如何工作的。

&`4b1101 = 0“和减少”如下所示:

1101

101

01

0但是,这个例子要复杂得多,我不明白。

回答 1

Stack Overflow用户

回答已采纳

发布于 2021-05-06 19:28:04

&counter[19:15] 与以下相同:

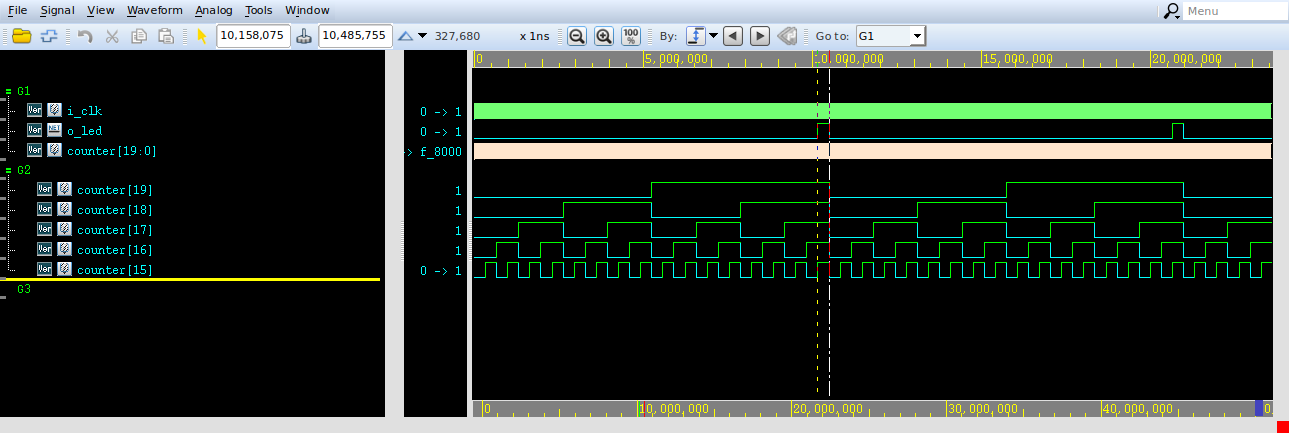

counter[19] & counter[18] & counter[17] & counter[16] & counter[15]缩减-和操作只是做了一些明智的,它的每一个比特。因此,只有当所有这5位o_led都很高时,您的counter信号才会很高,如下图中的游标(单击图像放大):

o_led的脉宽与您的缩减和表达式中的LSB匹配。在我上面的代码中,LSB是15。如果将LSB更改为16,则脉冲宽度会加倍。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/67424587

复制相关文章

相似问题