重新排序缓冲区问题(计算机体系结构乌达度课程)

有人能向我解释为什么I5指令的发布时间是第6周期,而不是根据为该问题提供的解决方案手册第5周期。

注: 1)问题及其已发表的解决方案如下2)此问题是关于Udacity的计算机体系结构课程的问题集的一部分。

问题:

使用Tomasulo的算法,对于以下顺序中的每条指令,确定它何时(在哪个周期中,从一开始计数)发出、开始执行,并将其结果写入CDB。假设一个指令的结果可以在它完成它的执行后写在它的周期中,并且一个依赖的指令可以(如果被选中)在之后的周期中开始它的执行。所有指令的执行时间是两个循环,除了乘法(需要4个循环)和除法(需要8个循环)之外。处理器具有一个乘法/除法单元和一个加/减单元。乘法/除法单元有两个预约站,加/减单元有四个预约站。没有一个执行单元是流水线式的,“每个执行单元一次只能执行一条指令。如果在选择应该开始执行的指令时发生了使用执行单元的冲突,则旧的指令(在程序顺序中前面出现的指令)具有优先权。如果发生使用CBD的冲突,则加/减单元的结果比乘/除单元的结果具有优先级。假设开始时所有指令都在指令队列中,但尚未向任何预订站发出任何指令。处理器每个周期只能发出一条指令,只有一个CDB用于写入结果。处理上述处理器中的异常的一种方法是,简单地从预订站和指令队列中删除所有指令,将所有拉特条目设置为指向寄存器文件,并尽快跳转到异常处理程序(即在检测到零除后的周期中)。1)找出每条指令的发布、选择和回溯的循环时间。2)如果以这种方式处理异常,将在异常处理程序中打印什么?

提供的解决办法:

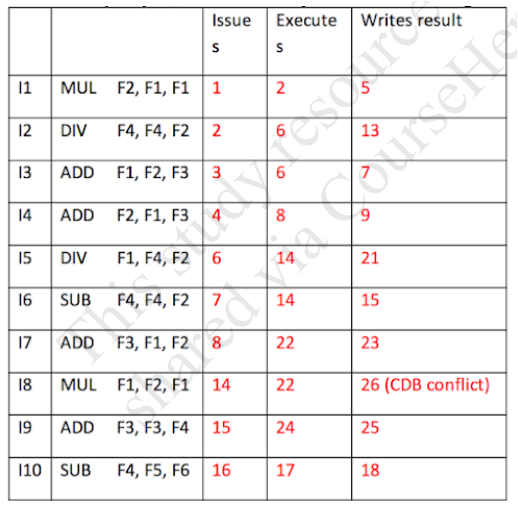

时序图

第二个问题的解决

异常发生在周期20中,因此我们开始执行异常处理程序的周期是21周期。当时,处理器已经完成了指令I1-I4,但也完成了指令I6和I10。因此,寄存器文件中的寄存器F4将具有I10的结果,即-1 (5-6)。异常处理程序将打印2,0,-2,-1,这是不正确的。

回答 1

Stack Overflow用户

发布于 2021-06-02 01:25:23

是否有一个有限的ROB或RS (调度程序)大小将阻止前端发出更多的指令,直到一些人已经派出更多的空间(RS大小),或直到一些退休(ROB大小)?前端最好的情况是比后端更好的吞吐量是很常见的,因此后端稍后可以查看可能的独立指令。但是,对于后端可以跟踪多少未执行的指令,必须有一定的限制。

在这种情况下,是的:

乘/除单元有两个预约站,加/减单元有四个预约站。

所以我认为这是限制因素:前两个指令是mul和div,第一个指令是在循环5中完成的。显然,这个CPU在写完后的循环之前不会释放RS条目。(而不是一个统一的调度器,而是为每种执行单元分别设置队列(预订站)。)

一些真正的CPU可能更具侵略性,例如,我认为Intel CPU可以更快地释放RS条目,即使它们有时需要重播一个uop,如果它是在预期缓存命中(当输入是负载的结果)而提前发送的话:Are load ops deallocated from the RS when they dispatch, complete or some other time?:

https://stackoverflow.com/questions/67790063

复制相似问题