延迟计数器不递增?FSM

延迟计数器不递增?FSM

提问于 2021-09-13 11:22:18

我正在为DAC寄存器编写代码,需要延迟。但是,在延迟状态下,DAC_counter_2没有递增,延迟也没有实现。我已将代码复制到不同的项目,并试图检查。这个问题仍然存在。任何帮助都会很好。

module dac_card

( output reg DAC_SCLK,

output reg SYNC,

output reg SDIN,

input MHZ_50_CLK,

input RST,

output reg [7:0] DAC_counter_1,

output reg [7:0] DAC_counter_2

);

reg [7:0] pst_state, nxt_state;

reg [23:0] DAC_reg;

always @(posedge MHZ_50_CLK)

begin

if (RST)

begin

DAC_reg <= 24'hEEEEEE;

SYNC <= 1'b1;

DAC_SCLK <= 1'b0;

SDIN <=1'b0;

DAC_counter_1 <= 8'd0;

DAC_counter_2 <= 8'd0;

pst_state <= 8'd0;

end

else

begin

pst_state <= nxt_state;

DAC_counter_1 <= DAC_counter_1 + 1'b1;

end

end

always @(pst_state or DAC_counter_2)

begin

case (pst_state)

8'd0 : begin

if (DAC_counter_2 == 8'd24)

begin

DAC_counter_2 = 8'd0;

SYNC = 1'b1;

SDIN = 1'b0;

nxt_state = 8'd2;

end

else

begin

SYNC = 1'b0;

DAC_SCLK = 1'b1;

DAC_counter_2 = DAC_counter_2 + 1'b1;

SDIN = DAC_reg [23]; //Writing DAC register

DAC_reg = DAC_reg << 1;

nxt_state = 8'd1;

end

end

8'd1 : begin

DAC_SCLK = 1'b0;

nxt_state = 8'd0;

end

8'd2 : begin

if (DAC_counter_2 == 8'd10) //Minimum delay for SYNC to be low for write mode

begin

SYNC = 1'b1;

DAC_counter_2 = 8'd0;

nxt_state = 8'd3;

end

else

begin

SYNC = 1'b0;

//Not incrementing

DAC_counter_2 = DAC_counter_2 + 1'b1;

end

end

8'd3 : begin

nxt_state = 8'd0;

end

default : begin

nxt_state = 8'd0;

end

endcase

end

endmodule这是测试台

module test_bench

();

//Analog Card DAC wires and registers

reg MHZ_50_CLK;

reg RST;

wire DAC_SCLK;

wire SYNC;

wire SDIN;

wire [7:0] DAC_counter_1;

wire [7:0] DAC_counter_2;

//Instatntiate DAC

dac_card dc (.DAC_SCLK(DAC_SCLK),

.SYNC(SYNC),

.SDIN(SDIN),

.MHZ_50_CLK(MHZ_50_CLK),

.RST(RST),

.DAC_counter_1(DAC_counter_1),

.DAC_counter_2(DAC_counter_2)

);

initial

begin

MHZ_50_CLK = 1'b0;

#10 RST = 1'b1;

#20 RST = 1'b0;

end

always

begin

#10 MHZ_50_CLK <= ~MHZ_50_CLK;

end

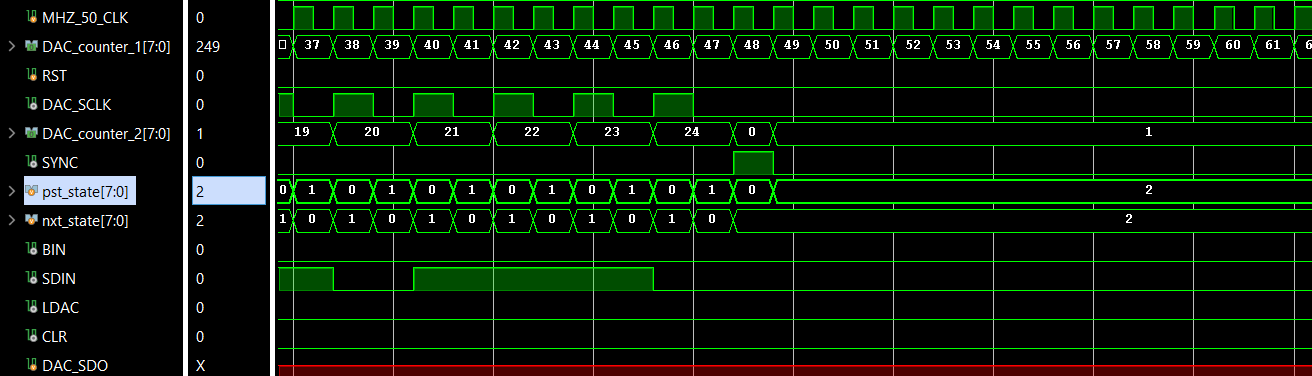

endmodule这是波形。在24次DAC_counter_2计数后,8'd10的延迟没有实现。

回答 1

Stack Overflow用户

回答已采纳

发布于 2021-09-13 12:02:54

您需要在nxt_state语句的所有分支中为case分配一个任务。这也避免了推断出意外的闩锁。例如,请参阅下面的// MISSING nxt_state =行:

8'd2 : begin

if (DAC_counter_2 == 8'd10) //Minimum delay for SYNC to be low for write mode

begin

SYNC = 1'b1;

DAC_counter_2 = 8'd0;

nxt_state = 8'd3;

end

else

begin

SYNC = 1'b0;

//Not incrementing

DAC_counter_2 = DAC_counter_2 + 1'b1;

// MISSING nxt_state =

end

end正如您的波形所显示的,一旦进入状态2,您将保持状态2。由于状态2中的DAC_counter_2不是10,所以始终执行else子句,该子句不会更改nxt_state。

还有几个其他问题也可能造成问题。

良好的编码实践建议从单个reg块向always分配任务。DAC_counter_2被分配在两个不同的块中。

同样的,同样的信号不应该同时出现在组合always块中赋值的LHS和RHS上,因为它创建了一个反馈循环。例如,DAC_counter_2 = DAC_counter_2 + 1可能处于像DAC_counter_1这样的顺序always块中。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/69161791

复制相关文章

相似问题