如何实现无符号4位乘法器的代码?

如何实现无符号4位乘法器的代码?

提问于 2022-10-04 05:14:06

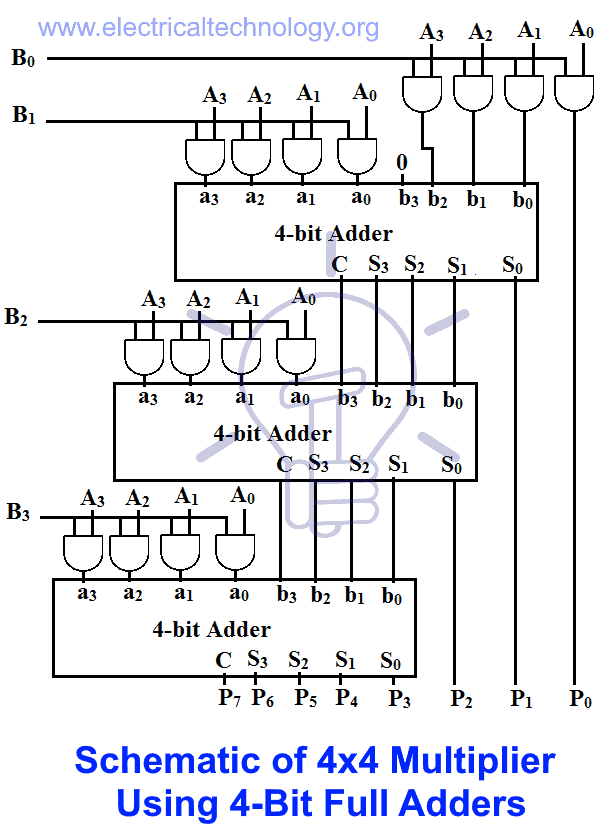

我试图创建一个4位乘子使用行为Verilog,如果可能的话,使用赋值语句和过程块。我试图复制的电路是这样的:

到目前为止,我定义了子模块fouralu_adder,它是一个简单的无符号4位加法器.然后我编写了以下psuedo代码:

module fouralu_multi(

input [3:0] A_i,//Input signals

input [3:0] B_i,

output [7:0] S_o//Output signal

);

wire [4:0] S1,S2;//These were supposed to be the SUM wires coming out of AD1 and AD2

wire [3:0] AND;

fouralu_adder AD1(

//Port connections here

);

fouralu_adder AD2(

//Port connections here

);

fouralu_adder AD3(

//Port connections here

);

endmodule我最初的想法是以某种方式分配和门的行为,比如:assign AND = A_i&B_i[0];,然后对B_i的每个值进行重复,但很快就意识到这是一种效率很低的方法。这就引出了一个问题:如何使用行为verilog实现电路?如何将输入端口连接到子模块,而不使用结构化verilog,并且使用尽可能少的wire变量?预先感谢您的帮助

回答 1

Stack Overflow用户

回答已采纳

发布于 2022-10-06 04:22:51

你可以使用for循环,谷歌它,你将学习如何使用它。

例如

integer idx;

reg [3:0] A_AND_B [0:3];

always @(*)begin

for( idx=0; idx<4; idx=idx+1) A_AND_B[idx] = {4{B[idx]}} & A;

end此代码等于

reg [3:0] A_AND_B [0:3];

always @(*)begin

A_AND_B[0] = {4{B[0]}} & A;

A_AND_B[1] = {4{B[1]}} & A;

A_AND_B[2] = {4{B[2]}} & A;

A_AND_B[3] = {4{B[3]}} & A;

end页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/73943361

复制相关文章

相似问题