我怎么可能知道ETH不会使用AXI SRAM呢?SDMMC2也是一样的吗?STM32H745

不久前,我为了好玩写了自己的以太网驱动程序,大部分时间都用在键盘上敲我的头,因为它不工作--这是传统。

问题是以太网根本无法读取或写入AXI SRAM。我在st的社区上做了一个很长的关于它的帖子 (以及其他一些事情),这个问题没有得到回答,我最终忘记了它。

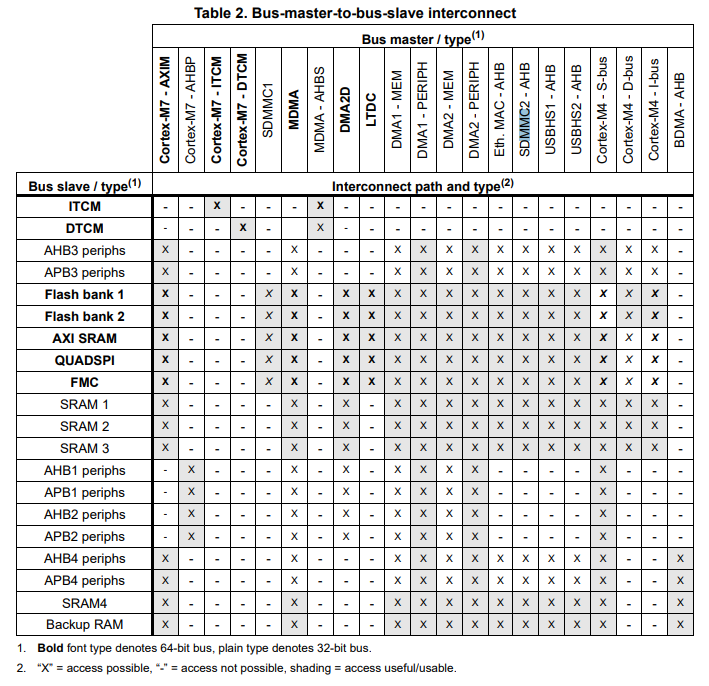

我问你为什么我应该知道这件事,是因为它似乎在任何地方都没有提到。总线互连表和图表似乎没有显示任何潜在的问题:

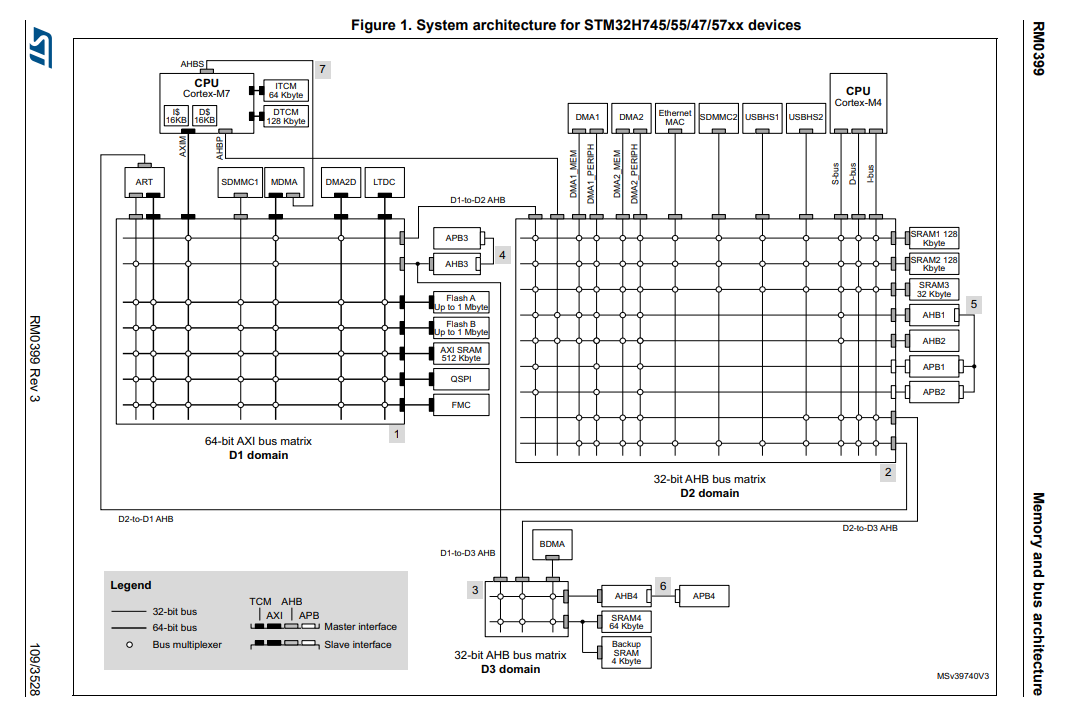

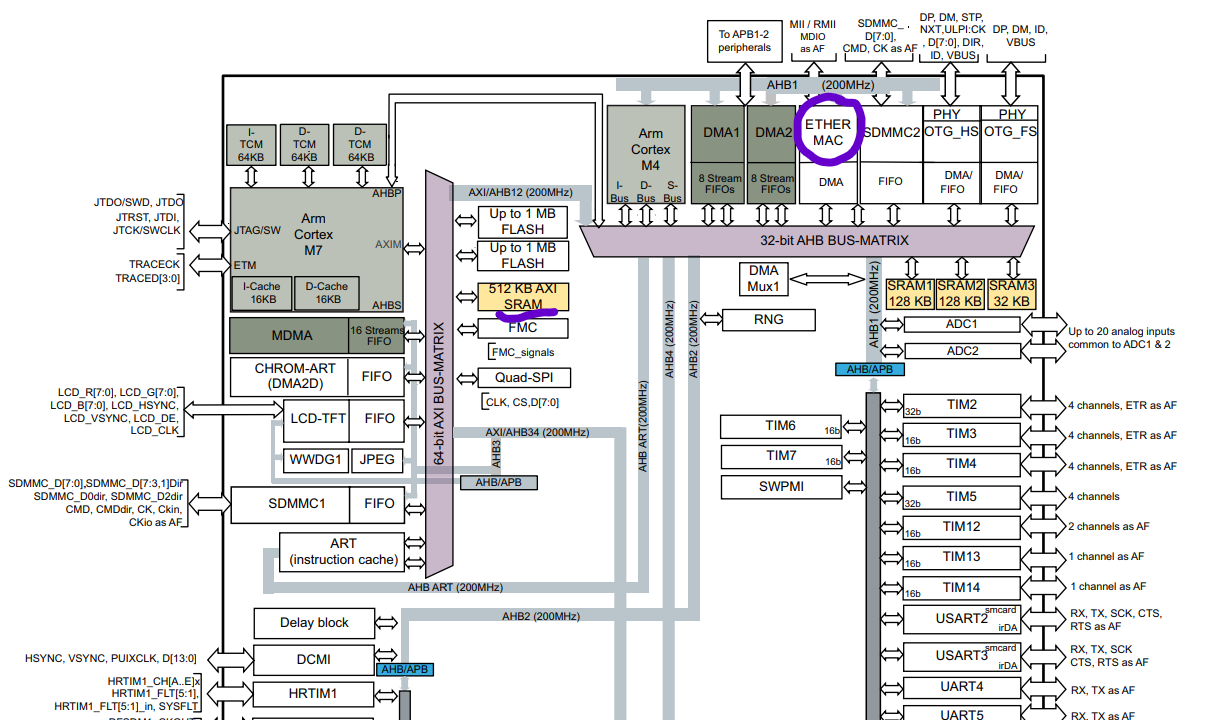

和方框图:

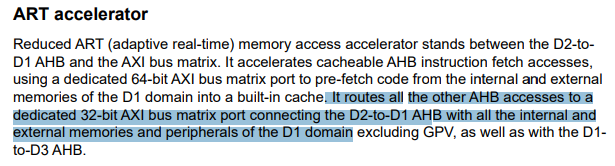

也许艺术并不是我对此的解读:

但我的解释是,它充当了一个加速器,用于从D1内存(和)中预先获取将由处理器执行的指令,以建立与D1内存的一般连接。

难道这只是我不知道“访问”这个词的意思吗?英语不是我的第一语言,但我很确定当你“接触到”一些东西,这意味着你可以玩它,所以阅读和写作。

这么久后,我才想起这一点,因为现在我想用SD卡来做我正在做的事情,我发现有必要从D2内存写入卡,然后从卡写入D1内存。

SDMMC1是不可能的,因为它甚至不能与D2内存交互,对于SDMMC2,我恐怕会有与以太网相同的场景。

我意识到我仍然可以正常地处理周围的事情,但这是相当多的额外的复杂性和额外的内存使用。

那么-我错过了什么会让我知道我不能以太网-dma进入axi sram?我是否应该期望它也能阻止我进入axi?

谢谢!

回答 1

Stack Overflow用户

发布于 2022-09-18 13:21:15

我没有编写自己的驱动程序,而是在CM7核上使用了Cyclone /IP堆栈。在尝试将缓冲区/描述符放入SRAM4时,我也遇到了同样的问题。

我观察到ETH_DMACSR所有的REB,TEB和FBE位被设置为1,在切换到SRAM3之后,所有这些都是有害的。

不幸的是,我无法回答您的问题,也无法说明SDMMC将如何工作:(

https://stackoverflow.com/questions/73679953

复制相似问题