线值不受指令的影响。

线值不受指令的影响。

提问于 2022-07-21 01:59:36

这是我的设计,calH.v

module calH(

input clk,

input rst,

input [1:0] xin,

input [15:0] coeff, //4bit per coefficient

output reg [1:0] xout, //1 bit per x

output wire [7:0] H_value

);

reg [7:0] H_p; //processed H

always@(posedge clk or negedge rst) begin

if(~rst) begin //set initial condition

H_p <= 0;

end

else begin //cal H

H_p <= xin[0]*xin[0]*coeff[15 -: 4];

H_p <= xin[0]*xin[1]*coeff[11 -: 4];

H_p <= xin[1]*xin[0]*coeff[7 -: 4];

H_p <= xin[1]*xin[1]*coeff[3 -: 4];

end

end

assign H_value = H_p;

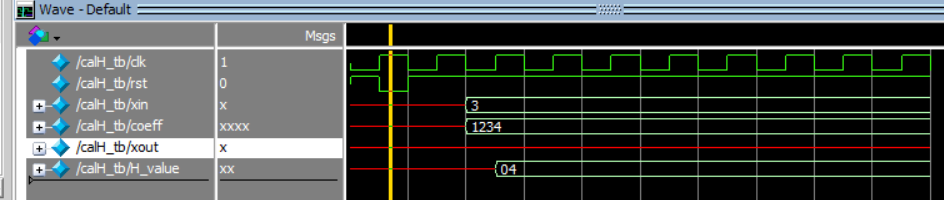

endmodule在“总是”中,H_p更改了四次,我指定了H_value = H_p,因此H_value也更改了四次。

在试验室中,我给出coeff =16‘h 1234;

在我的设计中,H_value结果应该是1->2 --> 3->4。

但是在modelsim仿真中,它只显示了4。谢谢。

回答 1

Stack Overflow用户

发布于 2022-07-21 02:55:42

变量H_p被覆盖3次;最后一次赋值获胜。

对该变量所做的所有更改都在0时间内发生在时钟的正边缘。

仿真不会显示覆盖,因为它发生在0次。

通过创建4个寄存器来保存4个输出,从而存储4个乘数的结果。如下所示:

module calH(

input clk,

input rst,

input [1:0] xin,

input [15:0] coeff, //4bit per coefficient

output reg [1:0] xout, //1 bit per x

output wire [7:0] H_value

);

reg [7:0] H_p_0; //processed H

reg [7:0] H_p_1; //processed H

reg [7:0] H_p_2; //processed H

reg [7:0] H_p_3; //processed H

always@(posedge clk or negedge rst) begin

if(~rst) begin //set initial condition

H_p_0 <= 0;

H_p_1 <= 0;

H_p_2 <= 0;

H_p_3 <= 0;

end

else begin //cal H

H_p_0 <= xin[0]*xin[0]*coeff[15 -: 4];

H_p_1 <= xin[0]*xin[1]*coeff[11 -: 4];

H_p_2 <= xin[1]*xin[0]*coeff[7 -: 4];

H_p_3 <= xin[1]*xin[1]*coeff[3 -: 4];

end

end

assign H_value = H_p_0;

// More assignments as needed

endmodule 然后根据需要组合这4个寄存器。

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/73059870

复制相关文章

相似问题