Intel IO APIC“建立APIC编程模型”

我正在阅读Intel处理器Z8000系列:数据表,第1卷。可以在这里找到https://cdrdv2.intel.com/v1/dl/getContent/332065。

对于IO APIC部分,说明IO APIC具有“建立APIC编程模型”的特点。Z8000系列数据表的两个卷都没有指定这是什么,我也找不到指定它的任何内容。

它指出有三个寄存器用于间接写入IO APIC的ID、VS和RTE寄存器。在IO APIC中RTE寄存器的形式在任何地方都没有讨论;我检查了数据表的两卷,以及Intel系统架构第三卷。3.我假设我必须遵循已建立的APIC编程模型?

我看过82093AA I/O文档https://web.archive.org/web/20161130153145/http://download.intel.com/design/chipsets/datashts/29056601.pdf。该文档似乎被用作引用IO APIC的大多数地方的源。

该文档是作为“已建立的APIC编程模型”的事实上的标准,还是有更多的功能?

回答 1

Stack Overflow用户

发布于 2022-06-27 16:29:30

它们是相同的,您发布的链接是is的参考数据表。

作为一个IO APIC,从软件的角度看,它只不过是一个查找表。所以规格没变。

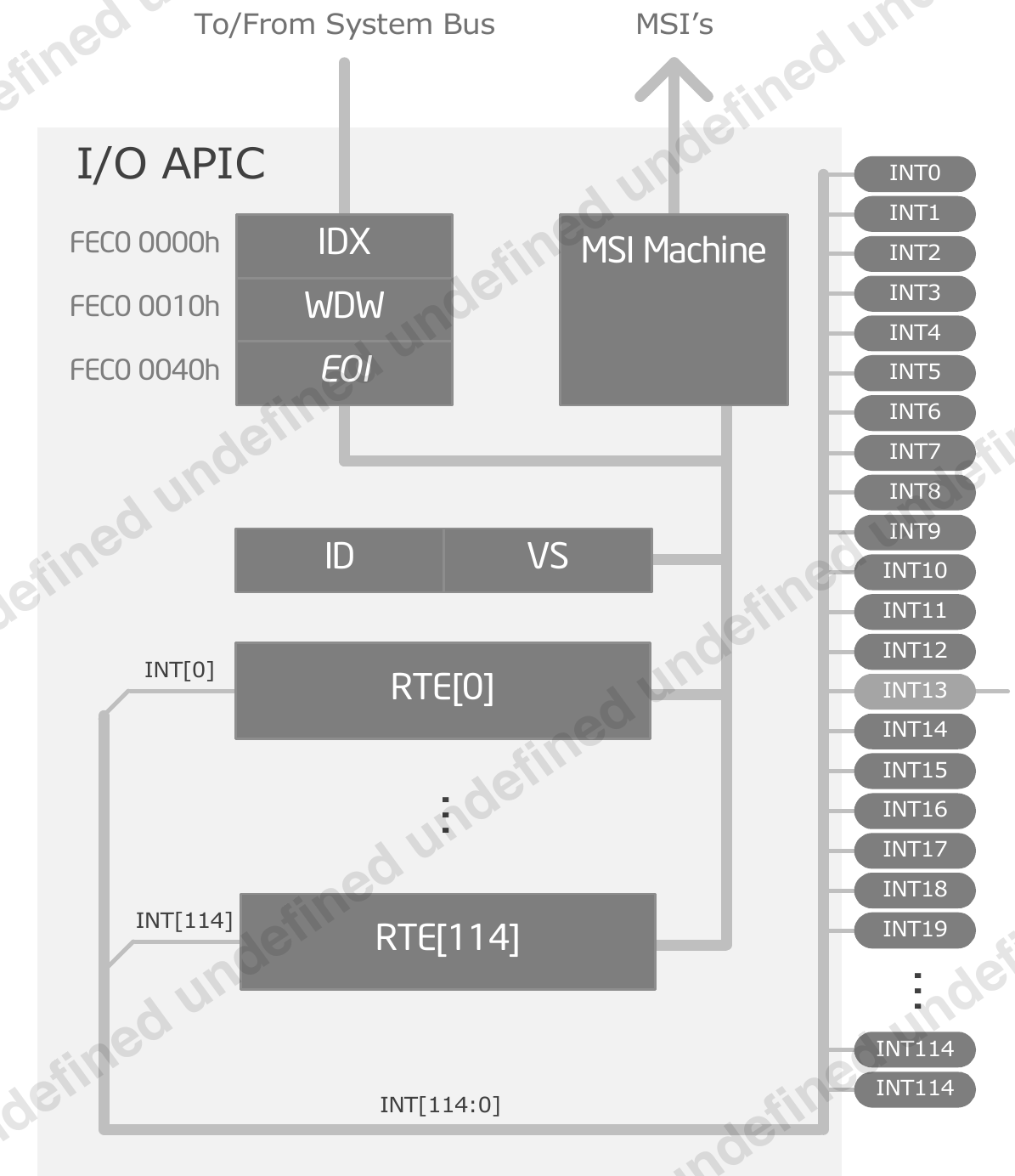

这张图片在Z8000数据表中

显示与您链接的IO数据表相同的功能。

是的,不同的命名是不幸的,但IO APIC可以追溯到1996年,同时许多工程师来了英特尔公司。

寄存器偏移匹配。

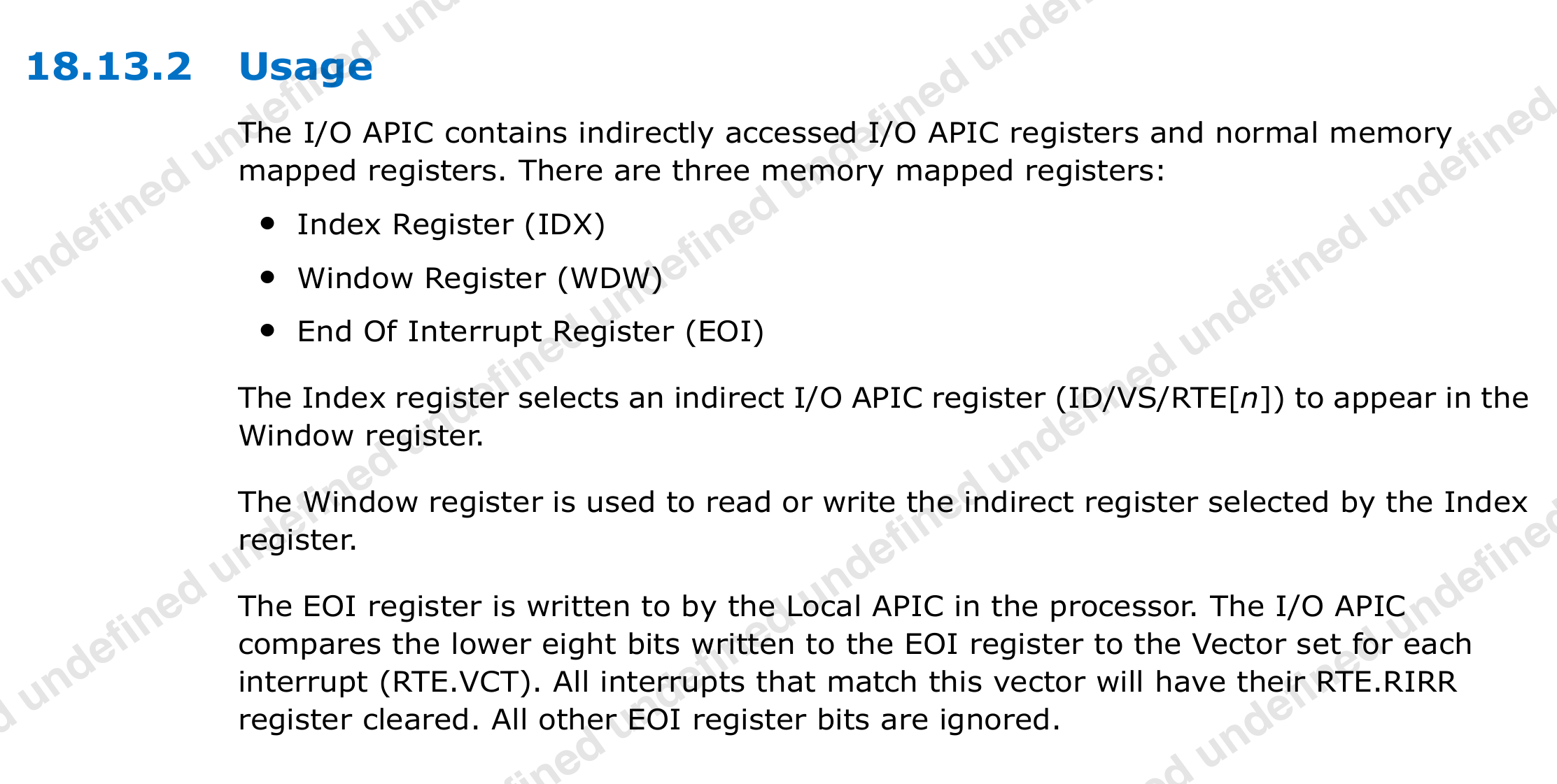

无论如何,Z8000数据表描述了寄存器(我使用了一张图片,因为我可以从PDF复制粘贴):

唯一的新细节是EOI寄存器。由于布兰登指出英特尔更新了x2APIC规范的LAPIC接口(注意LAPIC,而不是IO接口)。

这包括一个有向EOI特性,其中操作系统配置LAPIC 而不是以将EOI发送到任何IO。操作系统将负责向LAPIC和IO发送EOI信号。

Z8000支持这两种模式:向IO写入EOI的LAPIC或OS。

数据表引用LAPIC进行写入的遗留模式。

最初的IO APIC使用专用总线与LAPIC ( APIC总线)通信。

该软件将通过中的EOI寄存器(注意:不是IO )发出中断结束的信号,而这反过来又会向IO发出信号。

由于APIC总线的消失,这个IO APIC实现有一个专门的EOI MMIO寄存器。

我想知道这个设计是否允许在不使用定向EOI时重新映射IO,我不知道LAPIC如何找到EOI寄存器的位置。

通常,据我所知,旧的IO有一个专用总线(因此他们不为EOI使用MMIO寄存器),而较新的IO要么位于uncore中,要么位于PCH或等效的后面(因此,它们对EOI在uncore总线或DMI上使用虚拟线协议)。

这似乎不同,SoC可能通过读取IO的配置基址将EOI消息转换为适当的MMIO寄存器。

实际上,这也适用于PCH后面和内核中的IO,因此所有最近的IO都有一个MMIO寄存器。

https://stackoverflow.com/questions/72772797

复制相似问题