无法获得用于GTKwaves的火箭芯片波形

无法获得用于GTKwaves的火箭芯片波形

提问于 2022-04-01 17:18:07

我想在火箭核上运行一个程序,并观察GTKwave中相应寄存器中的所有信号(例如PC、寄存器文件、ALU寄存器和线路等)。

然而,我唯一得到的(在芯片和火箭芯片)是一些奇怪的电线在GTKwave,我不能联系到核心/瓷砖。

我按照https://github.com/chipsalliance/rocket-chip上关于安装的说明进行操作。我能跑:

make CONFIG = freechips.rocketchip.system.TinyConfig (I did DefaultConfig as well)

make verilog

etc.此外,我还使用

make run-debug CONFIG= freechips.rocketchip.system.TinyConfig或带有hello word的特定文件。

对于每个文件,都有相应的*.out文件和所有已执行的指令,所以我天真地认为我可以运行任何这样生成的*.vcd,并查看所有指令的所有寄存器状态。

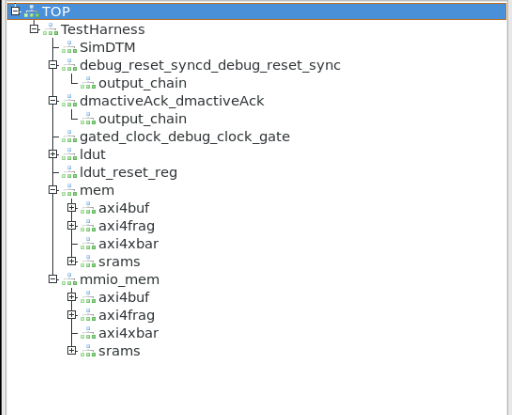

然而,我只得到奇怪的电线

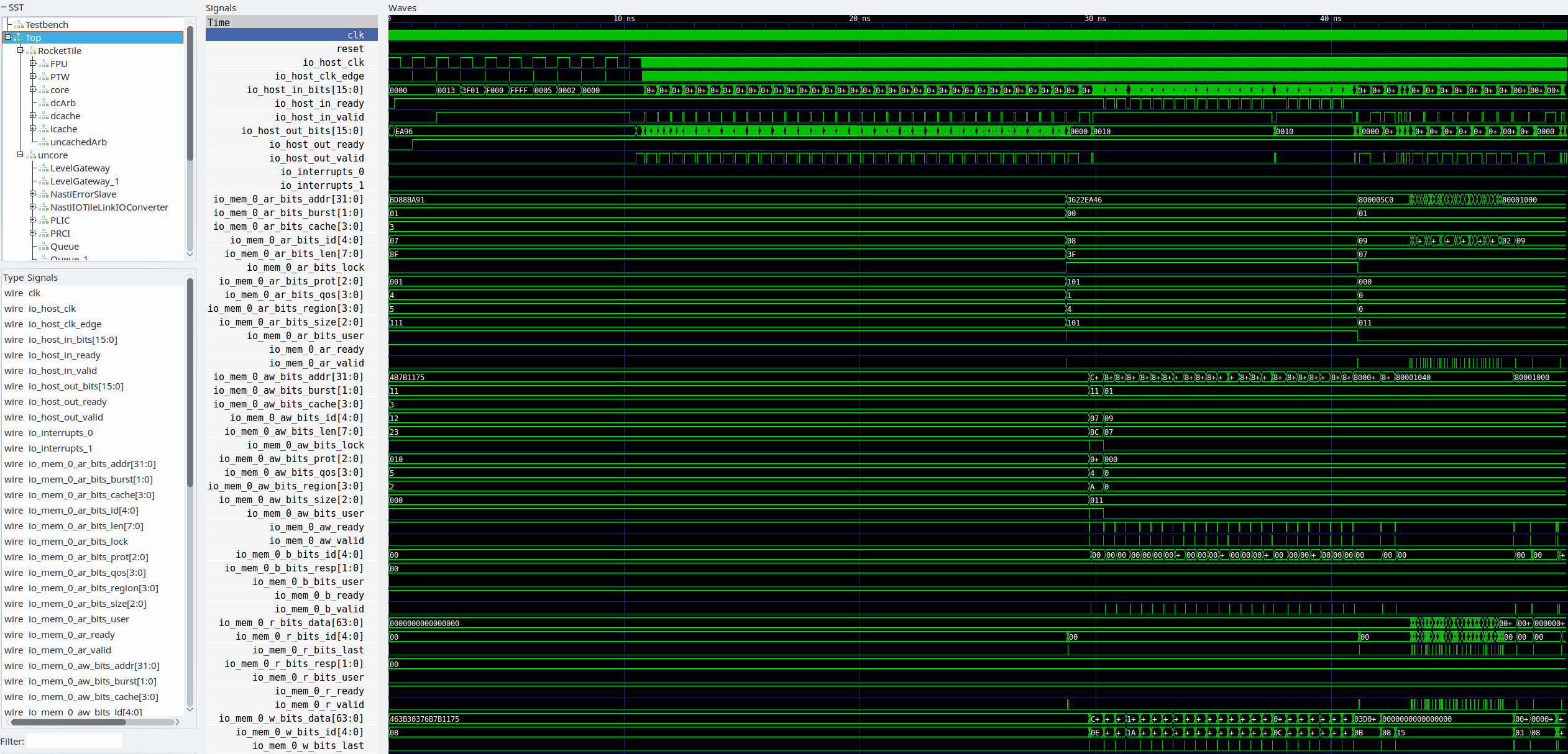

在其他地方,人们表现出这样的合理信号:

我观察了最后一张图片TestBench组。我用Quartus写的纯verilog测试了modelsim。但是对于火箭芯片框架,特别是Verilator,我认为我可以运行任何*.vcd文件。

对于我来说,它与论文第26页使用的方法相同,在第27页有合理的波浪。

有人能给我个提示吗,我的方法怎么了?

回答 1

Stack Overflow用户

发布于 2022-04-20 23:08:03

就像曾傑瑞在https://github.com/chipsalliance/rocket-chip/issues/2955上说的那样,你可以深入到层次结构中去寻找火箭核心和火箭瓷砖。你看到的电线是TestHarness。DUT是在测试之下的设计,其中包含火箭核心。

核心应该在如下的路径下:

ldut -> tile_prci_domain -> tile_reset_domain -> tile -> core

页面原文内容由Stack Overflow提供。腾讯云小微IT领域专用引擎提供翻译支持

原文链接:

https://stackoverflow.com/questions/71710629

复制相关文章

相似问题