ZYNQ PS与PL 数据交互方式

ZYNQ PS与PL 数据交互方式

FPGA技术江湖

发布于 2026-03-23 20:19:48

发布于 2026-03-23 20:19:48

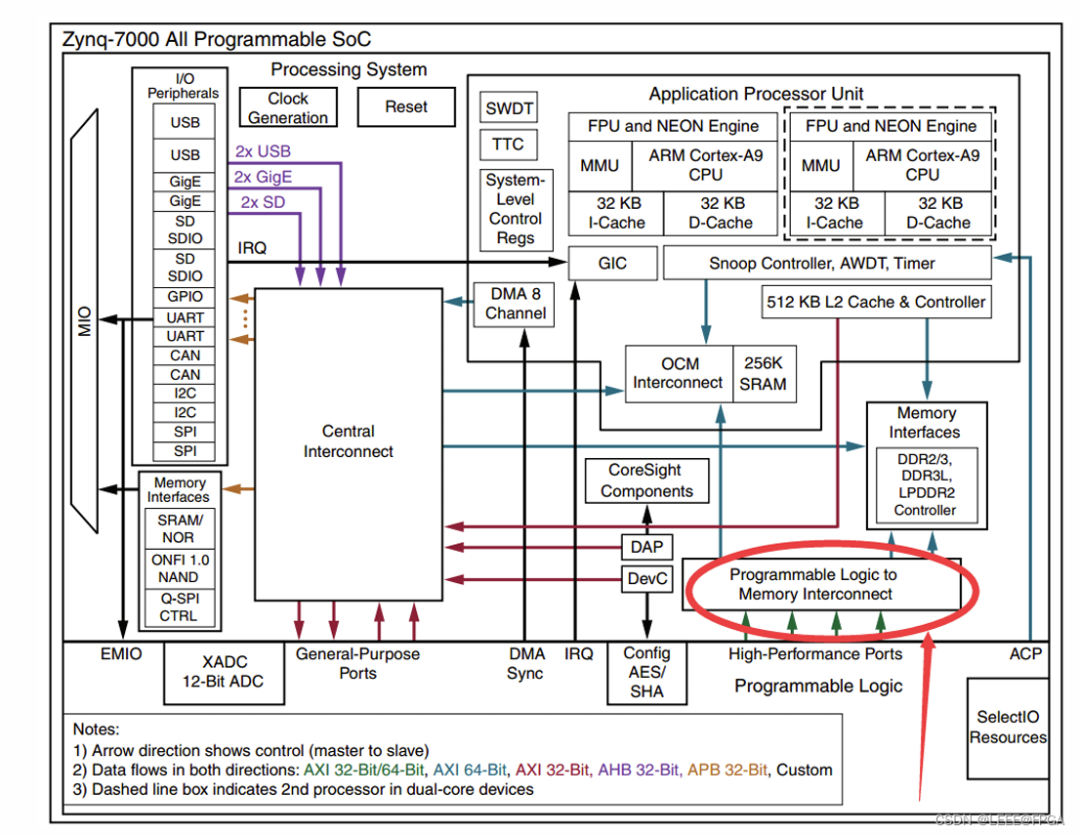

ZYNQ SoC 的 PS (Processing System) 和 PL (Programmable Logic) 之间的数据交互是系统设计的核心,以下是主要的交互方式及其特点:

一、AXI 总线接口

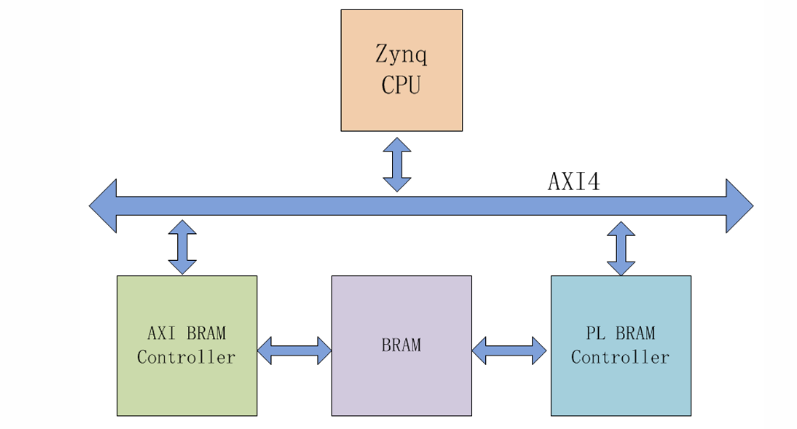

1. AXI4 高性能接口

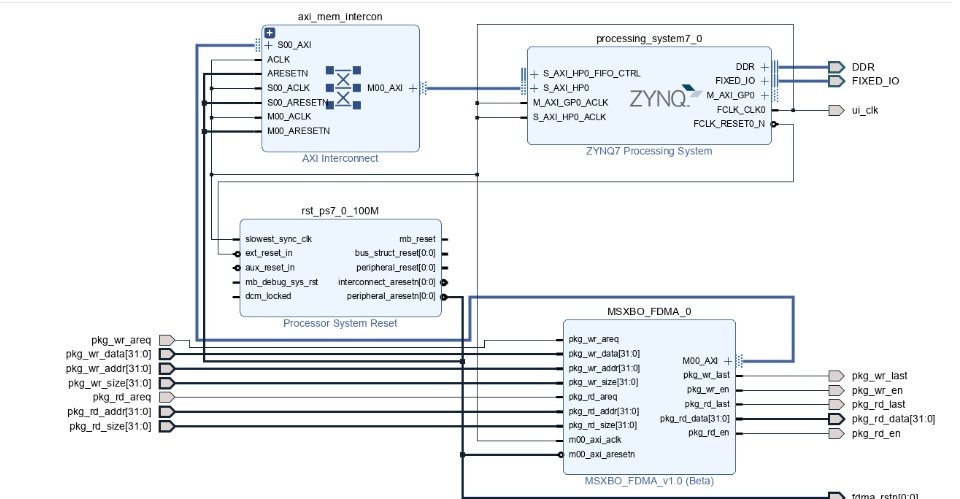

AXI4 (AXI4-Full) 用于高性能内存映射通信 支持突发传输,数据位宽通常为32/64/128/256/512位 典型应用:大数据量传输,如视频流、DMA传输 配置:通过HP (High Performance) 或 ACP (Accelerator Coherency Port) 端口

在这里插入图片描述

参考学习:ZYNQ AXI4 FDMA内存读写

https://leeefpga.blog.csdn.net/article/details/139261530

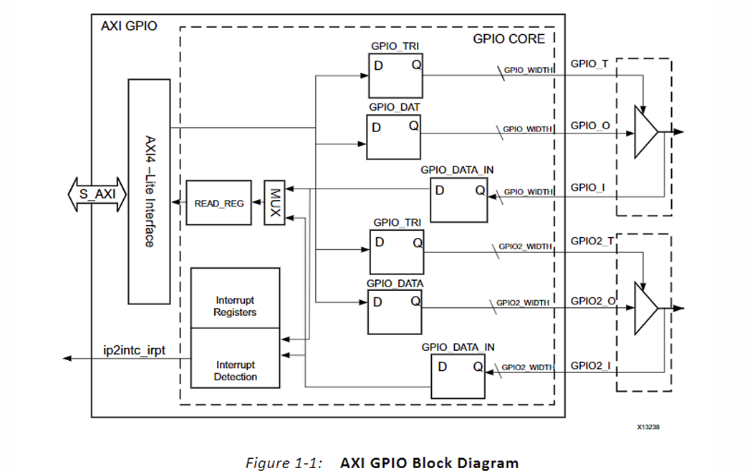

AXI4-Lite 简化版AXI,用于寄存器级访问 不支持突发传输,每次传输1个数据 典型应用:控制寄存器访问、状态监控 配置:通常通过GP (General Purpose) 端口 如 axi_gpio

在这里插入图片描述

在这里插入图片描述

参考学习:ZYNQ AXI GPIO

https://leeefpga.blog.csdn.net/article/details/136880196

ZYNQ 自定义AXI接口 IP(PWM)

https://leeefpga.blog.csdn.net/article/details/136940289

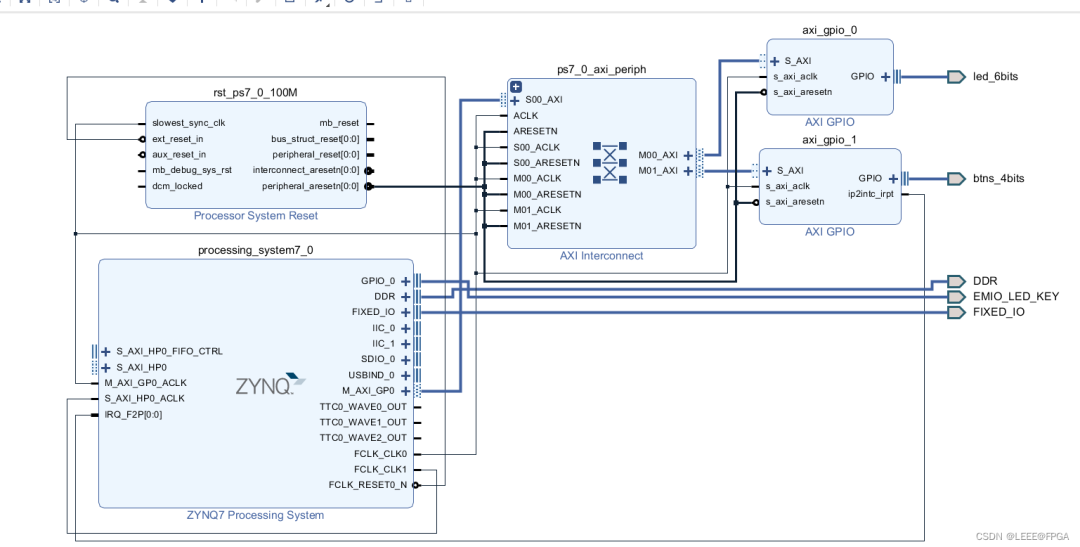

AXI4-Stream 无地址的流式数据接口 高性能连续数据传输 典型应用:视频流、ADC/DAC数据流

在这里插入图片描述

参考学习:ZYNQ VDMA IP学习

https://leeefpga.blog.csdn.net/article/details/140988072

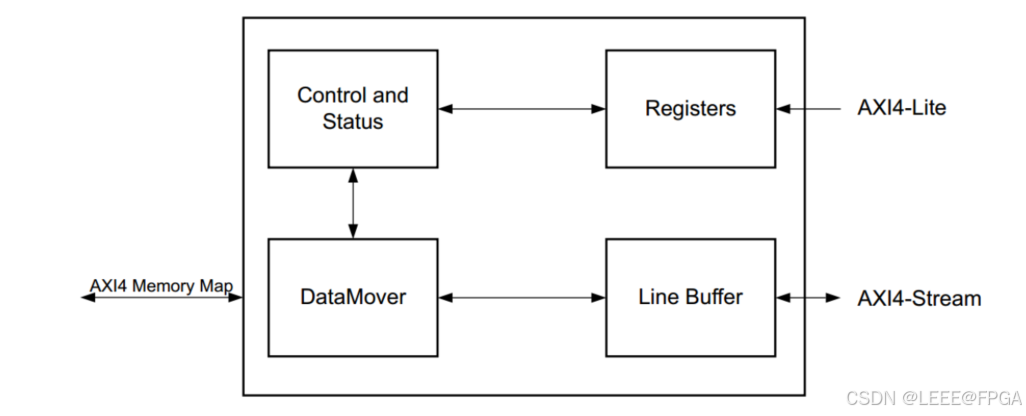

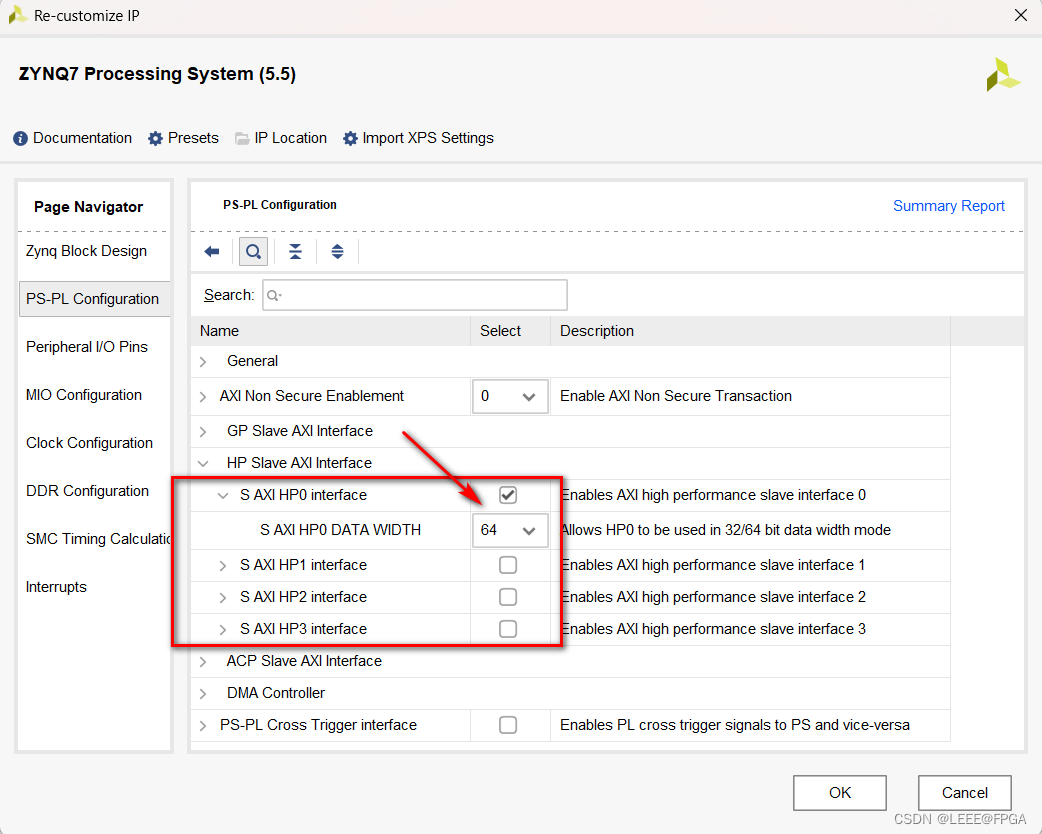

2. 专用AXI端口

HP端口 (High Performance) 4个HP端口(PS→PL) 支持64位数据宽度,最高可达1500MB/s(每个端口) 带FIFO缓冲,适合大数据量传输 ACP端口 (Accelerator Coherency Port) 1个ACP端口(双向) 保持与CPU缓存一致性 适合需要与CPU紧密协作的加速器

在这里插入图片描述

在这里插入图片描述

参考学习:ZYNQ–PL读写PS端DDR数据

https://leeefpga.blog.csdn.net/article/details/138107870

GP端口 (General Purpose)

4个主端口(PS→PL) + 2个从端口(PL→PS) 32位数据宽度,性能较低 适合控制信号和少量数据传输

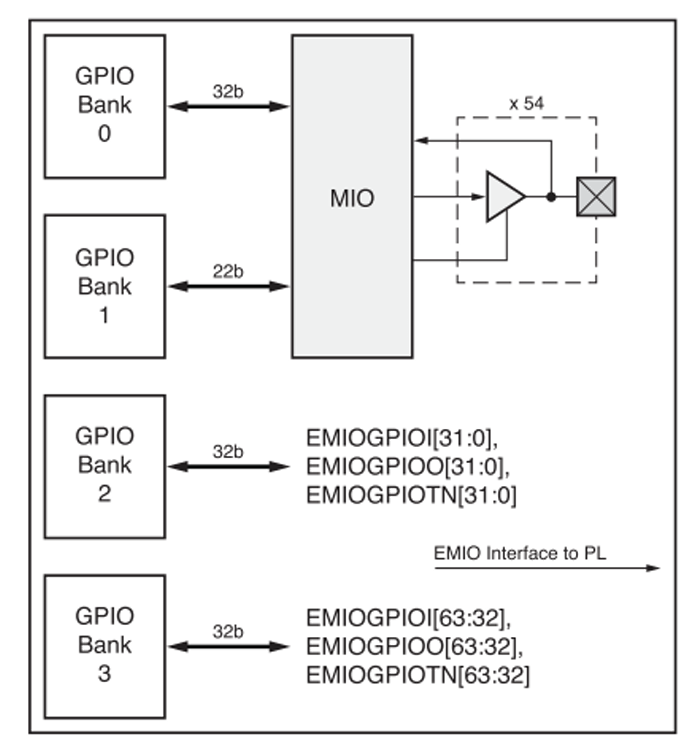

二、非AXI接口方式

1. EMIO (Extended Multiplexed I/O)

在这里插入图片描述

通过PS的I/O外设扩展至PL 支持GPIO、SPI、I2C、UART等外设接口 特点:配置灵活,但带宽有限

参考学习:ZYNQ学习(01) EMIO MIO

https://leeefpga.blog.csdn.net/article/details/136846551

ZYNQ PS端UART数据收发

https://leeefpga.blog.csdn.net/article/details/137007431

ZYNQ I2C 通信例程–EEPROM

https://leeefpga.blog.csdn.net/article/details/139081862

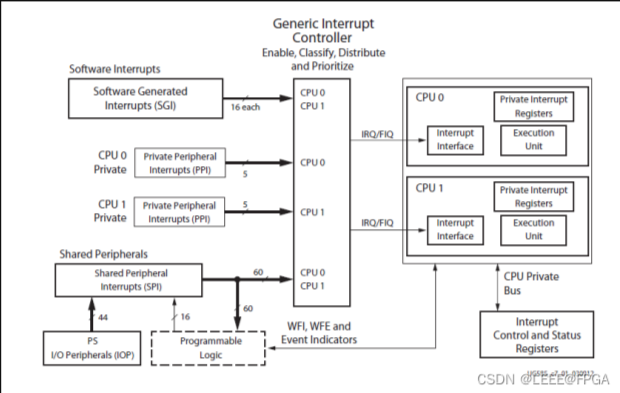

2. 中断机制 PL→PS中断

在这里插入图片描述

通过IRQ_F2P[15:0]引脚 支持电平触发和边沿触发 可用于事件通知、异常处理

参考学习:ZYNQ PL 中断请求

https://leeefpga.blog.csdn.net/article/details/134641174

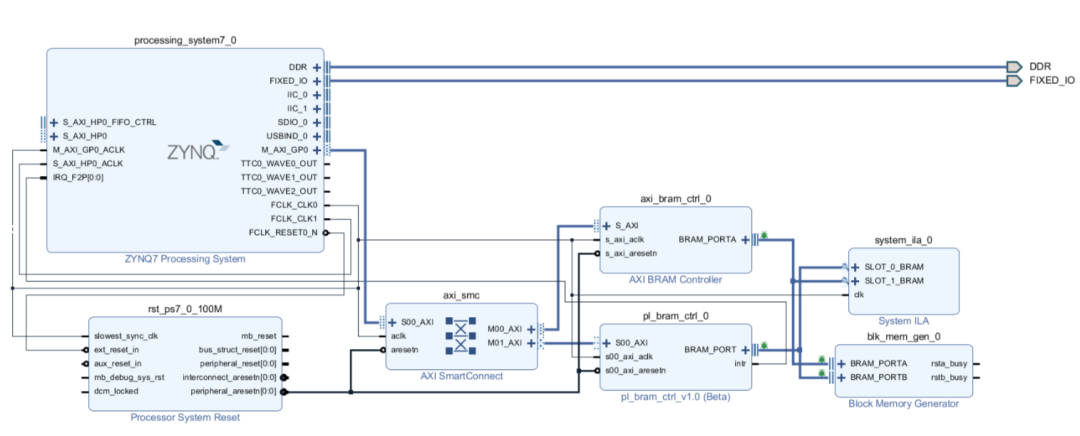

3. BRAM (Block RAM) 共享 通过PS和PL共享的片上存储器 高速低延迟访问 需要手动管理同步机制

在这里插入图片描述

在这里插入图片描述

参考学习: ZYNQ BRAM实现PS与PL数据交互

https://leeefpga.blog.csdn.net/article/details/138116215

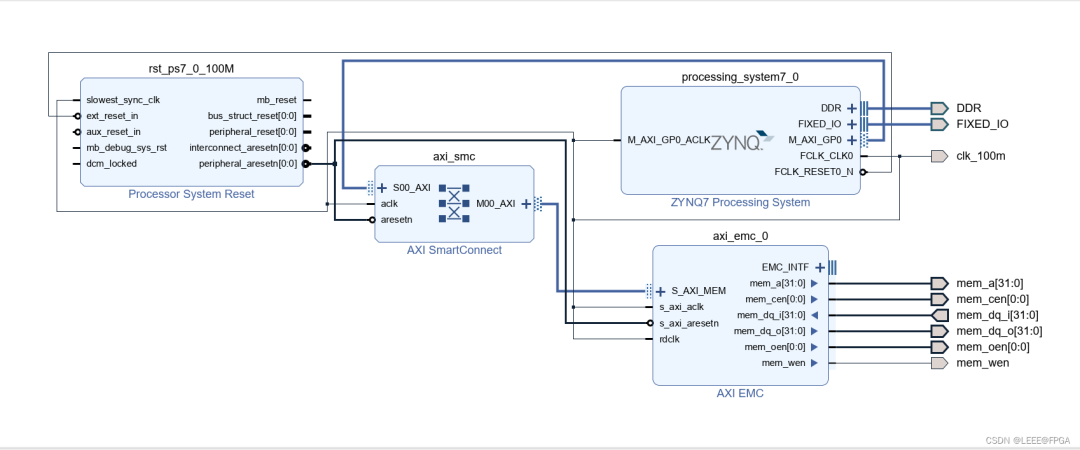

在这里插入图片描述

参考学习:ZYNQ EMIF进行PS与PL间的数据交互

https://leeefpga.blog.csdn.net/article/details/139289112

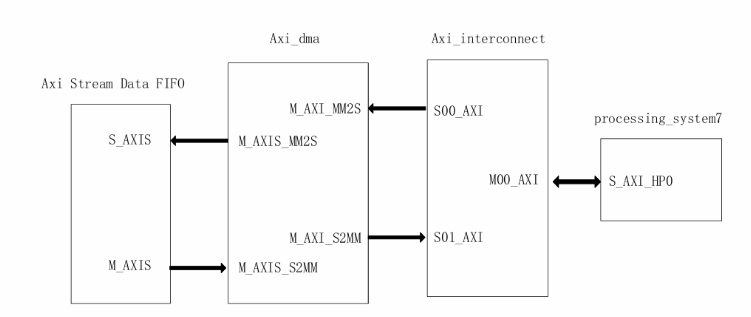

4. DMA传输 AXI DMA IP 支持内存与PL间高效数据传输 可配置为Scatter-Gather模式 减轻CPU负担,提高吞吐量

在这里插入图片描述

参考学习:ZYNQ DMA环通测试

https://leeefpga.blog.csdn.net/article/details/138147558

三、选择指南

在这里插入图片描述

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-10-13,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读

目录