Google TPU架构揭秘:OCS光交换,从4x4x4 Cube到9216卡Ironwood的进化引擎

Google TPU架构揭秘:OCS光交换,从4x4x4 Cube到9216卡Ironwood的进化引擎

AGI小咖

发布于 2025-12-17 14:02:37

发布于 2025-12-17 14:02:37

AGI小咖

本文深度复盘 Google TPU 智算集群的网络架构演进,重点剖析 3D Torus 拓扑与 OCS(光交换)技术的协同机制。 文章从最小拓扑单元 4x4x4 Cube 出发推演复盘 TPUv4 4096 Pod标准3D Torus环面与 TPUv7 9216 Pod的Twisted 3D Torus环面组网拓扑背后的原理和数学实现, 随后对比TPUv5e/v6e 的2D Torus Mesh性价比组网架构,揭示 Google 如何在万卡集群规模下实现确定性低延迟与极致 TCO(总拥有成本)优化,并对比 AWS 与 NVIDIA 的异构技术路线 ,结合上下游供应链生态与CPO技术趋势分析,展望未来TPU架构“芯片出光、全光直连”全新范式。

1

TPU超节点演进前序回顾

《Google TPU前世今生:从AlphaGo到9216卡Ironwood超节点,媲美英伟达》文章中我们分享了从 AlphaGo 背后 TPUv1 演进至OCS+ ICI + 3D Torus 加持、媲美 GB200/GB300的 TPUv7(9216卡Ironwood超节点),同时对比阿里和英伟达,马太效应和正向飞轮下谁才是AI时代既租售铲子又挖金子的主。

接下来我们基于48台OCS如何撑起4096卡的TPU集群Google TPUv4 pod的Google发布的论文为奇点,剥洋葱式一步一步串讲4096卡TPUv4集群到最新的9216卡TPUv7集群,以及背后的2/3D Torus + OCS光交换 + ICI网络演进和上下游成熟产业链相得益彰。

2

基石:TPUv4 与3D Torus/OCS 实现

4096卡的TPU集群TPUv4 Pod是Google OCS光交换网络架构成熟应用非常经典的一个标志性产品,也是我们为数不多在公开渠道能够看得到经典应用案例,接下来我们从最小单元模块出发推演至宏观的集群架构。

2.1 最小拓扑单元:4×4×4Cube(立方体)

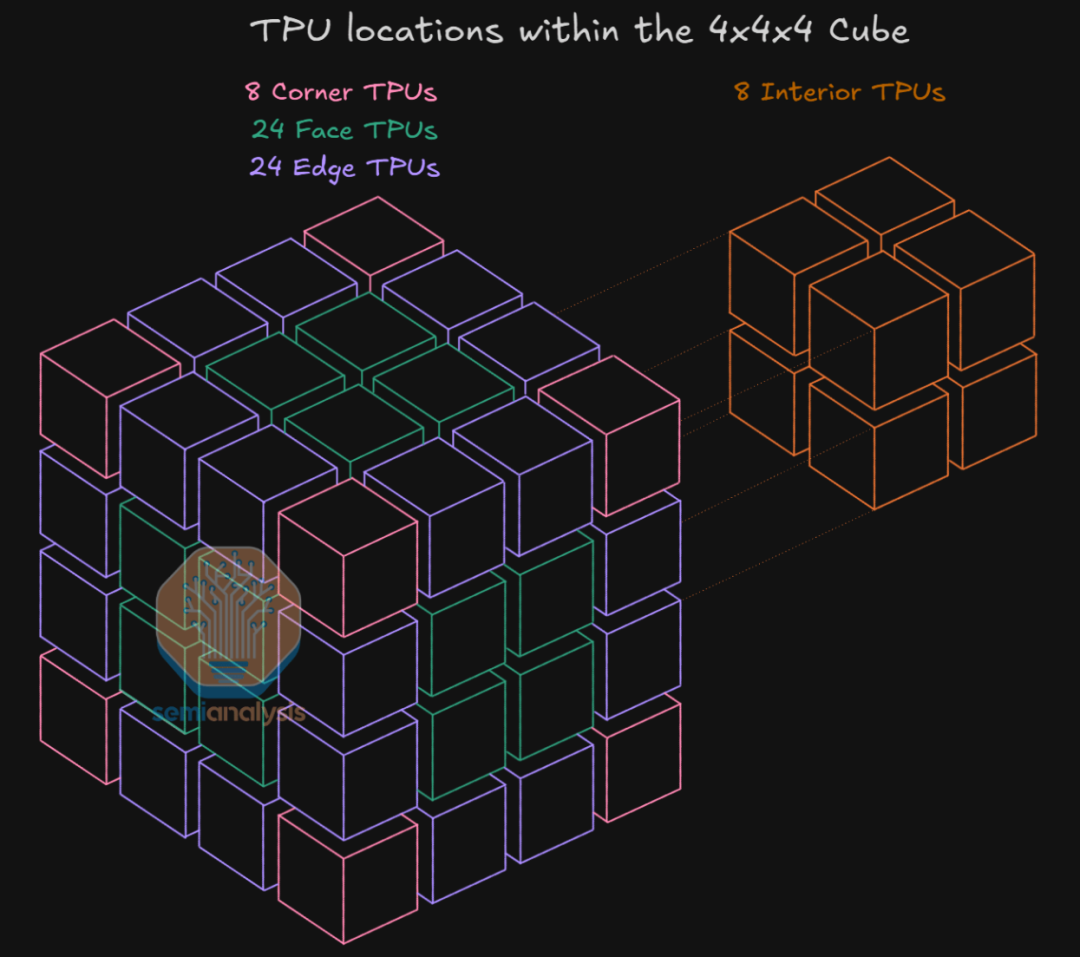

Google TPUv4 Pod架构组网中的最小拓扑单元是TPU Cube(或 4×4×4 Cube),虽然物理形态上通常对应一个服务器机柜,但在逻辑上它是一个严密的整体:

- 单元组成:由 4 (X) × 4 (Y) × 4 (Z) 共 64 块 TPU 芯片构成,看起来像是一个实心的“四阶魔方”。

- 链路总数:每块 TPU 芯片引出 6 条 ICI (Inter-Chip Interconnect) 高速互联链路,分别对应三维坐标系的 ±X, ±Y, ±Z 六个方向,构建起 3D Torus 的基础网格。

2.2 单个Cube链路分层与光电边界分析

在一个 4×4×4 的标准Cube中,ICI 链路根据物理位置和传输介质被严格划分为两类,构成了TPU架构独特的光电混合网络:

- 内部互联(魔方内核):位于立方体内部(包括内核、和非暴露面)的链路,通过极短的 PCB 背板与铜缆 实现全电信号互联,不经过OCS交换机,无需光电转换。

- 外部互联(魔方表面):仅有位于立方体六个外表面的链路会被引出(包含顶点、棱边和表面中心的向外链路),单个Cube合计对外引出 96 条光互联链路连接至OCS光交换机,从而实现Cube与Cube之间的动态路由与超大规模扩展,具体计算过程如下:

图1 TPUv4 4x4x4Cube互联逻辑与光电接口分布

TPU位置类型 | 数量(个) | 几何特征 | 内部铜缆链路数 | 外部光纤链路数 | 单Cube光链路总数 |

|---|---|---|---|---|---|

顶点(红色) | 8 | 立方体8个顶点 | 3 | 3 | 8*3=24 |

棱边(蓝色) | 24 | 12条棱的中间 | 4 | 2 | 24*2=48 |

中心面(绿色) | 24 | 6个面的中心 | 5 | 1 | 24*1=24 |

内核心 | 8 | 被包裹在核心内 | 6 | 0 | 8*0=0 |

总计 | 64 | 96 |

表1:TPUv4 4*4*4 Cube的96条光链路推算过程

2.3 TPUv4 Pod 集群48台OCS光交换机推演

上一章节中我们了解到TPUv4 Pod的最小拓扑单元为4x4x4 Cube即64颗芯片/Cube,那么为了构造4096个TPUv4 Pod的话,合计需要64个Cube。另外,按照每个96 Links/Cube核算,合计需要64 Cubes × 96 Links/Cube = 6144 条光链路。

Google公开的论文中提到其自研的PalomarOCS通常配置为 136 × 136 端口,但在工程上通常按 128 端口 有效容量计算(符合二进制 2^7 规整性,且预留 8 个冗余端口),因此所需的OCS数量为:6144 Links ÷ 128 Ports/OCS = 48 台 OCS。

为了在物理层严格控制和适配3D Torus,48台OCS被严格化为为三个正交组分别承载X/Y/Z轴不同维度的流量,以X轴组为例,包含16台OCS,遵循“同维互联”原则,每一台OCS仅仅负责连接和承载所有Cube上±X 面链路,构建 X 维度的环形闭环流量,依此类推Y轴组、Z轴组也一样采用物理正交隔离组网,确保了光路在动态重构时始终维持X/Y/Z三维空间的数学正交性,简化了上层软件路由算法和有效规避了网络死锁的风险。

在3D Torus环网中OCS 充当了巨大的动态配线架,负责物理实现 Torus 的几何特性,离开一个节点X+ 接口的数据,必然进入带有步长相邻节点(标准3D Torus组建TPUv4 Pod采用步长为1与相邻节点紧耦合标准环面,升级版3D Torus组建TPUv7 Pod采用可变步长N构建扭曲环面)的 X- 接口,对于处于网格边缘的TPU(例如坐标 X=End),其 X+ 接口通过OCS的光路调度物理直连回坐标 X=0 的TPU的 X- 接口形成 “首尾闭环”。

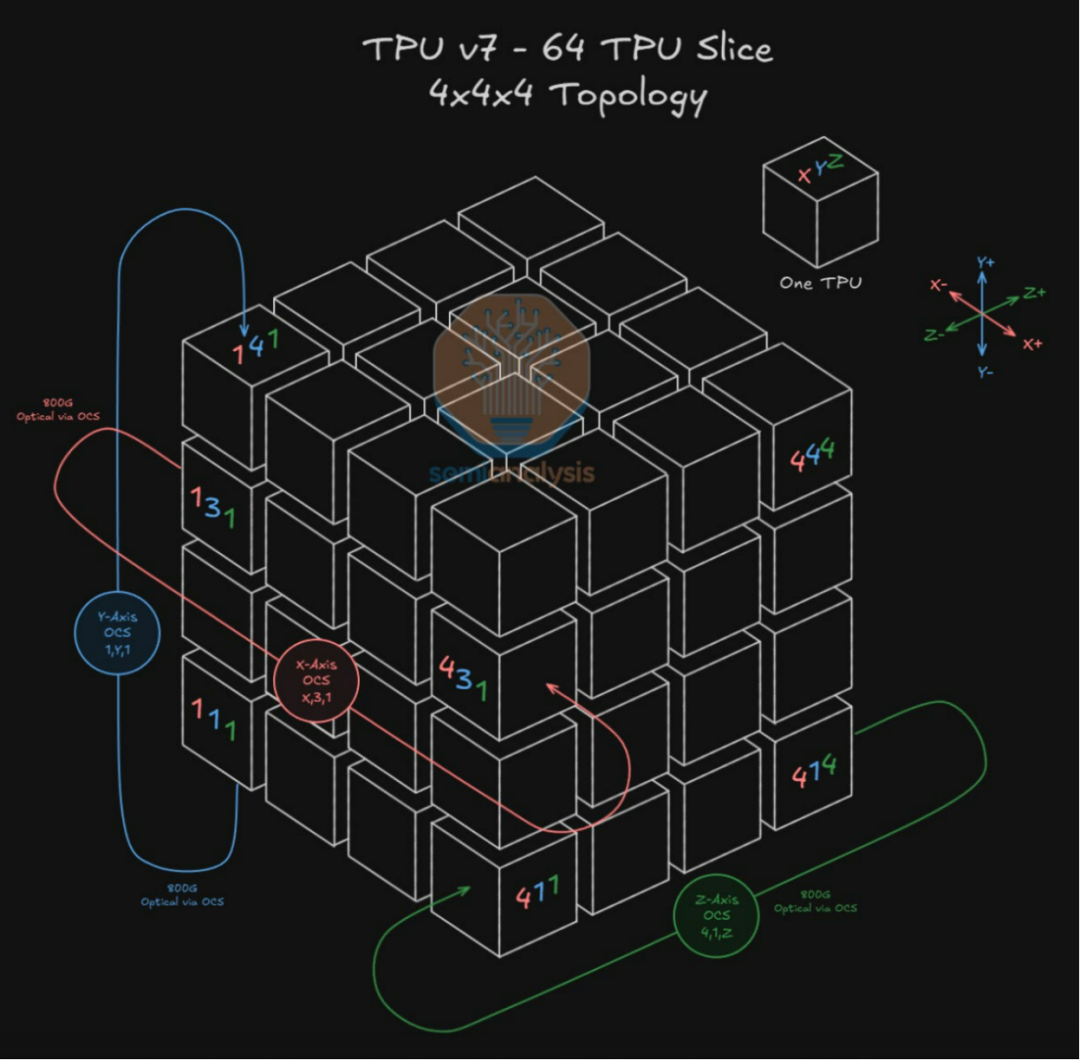

图2:TPUv7 64TPU的±X, ±Y, ±Z拓扑

2.4 TPUv4 Pod核心Palomar OCS微观构造

TPUv4 Pod组网架构中物理核心是Palomar OCS,与市面上无损网络交换机不同的是OCS不读取数据包头、不进行光电转化,仅仅只是物理层面的“光线反射镜”,在Palomar OCS机箱内部光信号的传输路径呈现出一个经典的“W”形状,最大限度减少插入损耗和实现任意端口间的互联。

图 3 OC SW形光路原理示意

W形光路设计 :光信号发送准直器 > 二向色分光镜 > 2D MEMS 阵列 I > 二向色分光镜 > 2D MEMS 阵列 II> 二向色分光镜 > 光信号接收Output 准直器。W形光路设计中的两大核心组件是2D MEMS和二向色分光镜,其中两级2D MEMS设计实现了三维空间内的精准光束操纵,二向色分光镜作为允许1310nm业务光透射,同时反射 850nm 监控光的核心滤光组件,与Injection Module + Camera Module联动实现实时带内运维监控和驱动2D MEMS的微秒级微调,这一套闭环控制和实时主动对准机制也是Palomar OCS能够大规模商用的核心壁垒之一。

3

架构演进:Twisted 3D Torus和2D Torus

随着单芯片TDP提升至600W且集群规模突破 9,216 卡,TPUv7 (Ironwood) 面临着更严峻的散热与延迟挑战,Google 在架构上进行了两项重大升级: 拓扑算法的扭曲 与 集群规模的极致扩张 。

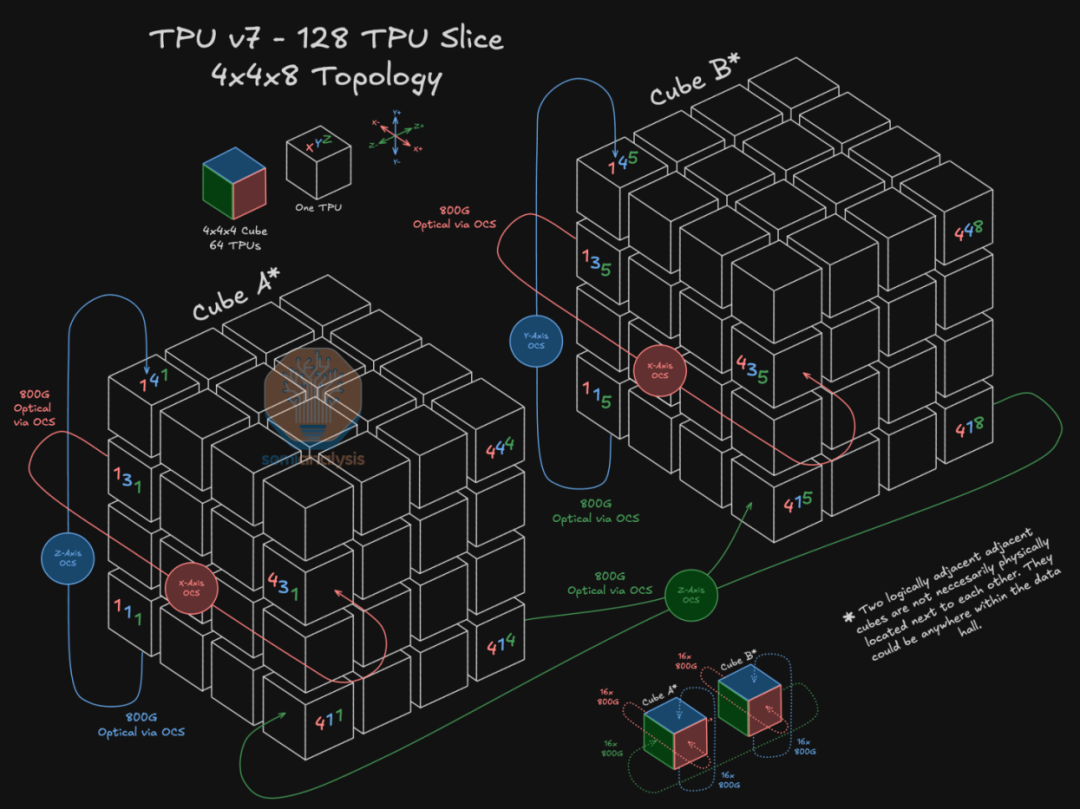

3.1 TPUv7 Twisted 3D Torus 拓扑和9216卡推演

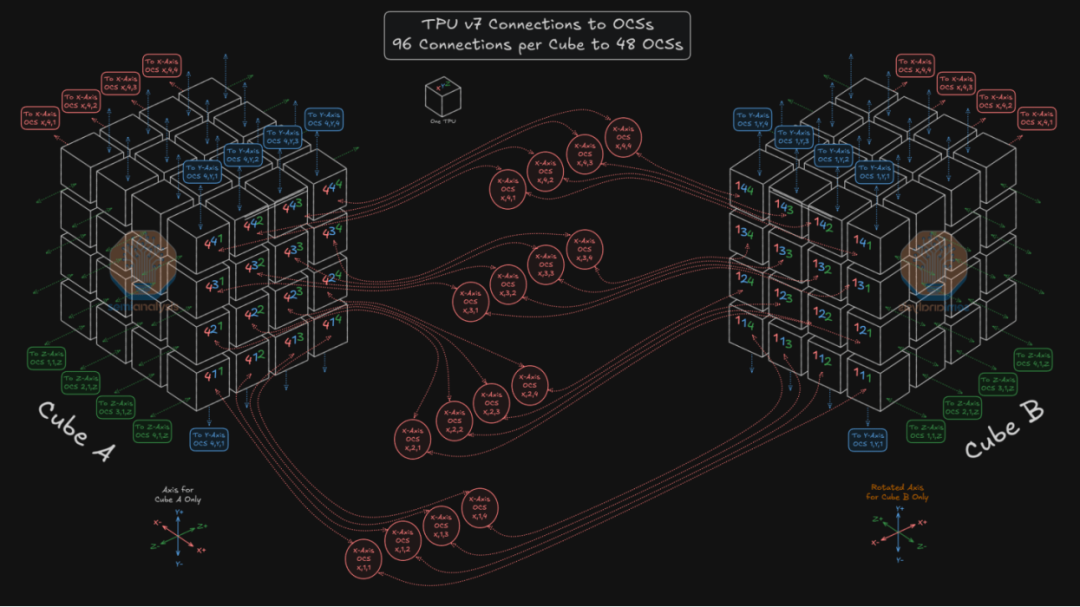

相比TPUv4 Pod的4096卡,TPUv7 Pod集群规模达到9216卡,其最小拓扑单元还是经典的4x4x4 Cube即64颗芯片/Cube,合计需要9216/64 =144 Cubes。另外,按照每个96 Links/Cube核算,合计需要144Cubes × 96 Links/Cube = 13,824 Ports。那么需要多少OCS呢?据称Google还是采用48台OCS,正如下图 "TPU v7 Connections to OCSs" 清晰地展示了 Cube A 如何将这 96 条链路扇出连接至中间的 48 台 OCS。

图4:TPUv7 Cube A与Cube B连接48台OCS

为了承接这一海量连接需求,Google 将每台 OCS 的规格升级为 144×144 端口(完美覆盖 144 个 Cube 的节点数,但从供应链端采购上看实际落地推测实际落地可能是320*320规格的OCS),同时将 OCS 与 Cubes 之间的Twisted 3D Torus连接带宽提升至 800G/1.6T,确保了超大规模集群下的无阻塞通信。

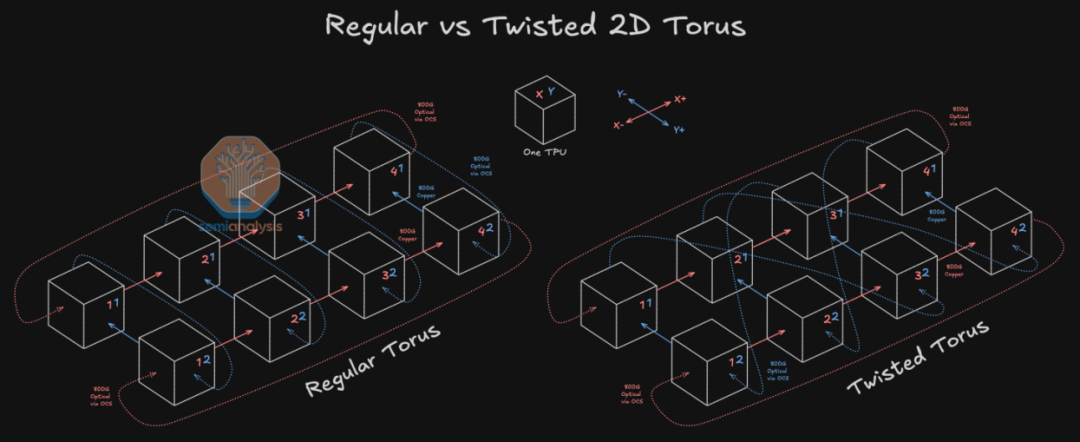

另外在拓扑结构上,TPUv7升级了标准的3D Torus,引入了步长的概念来构建了Twisted 3D Torus (扭曲环面) 拓扑以降低通信跳数,最优扭曲步长 N 通常由维度大小决定(公式近似为N ≈ Dimension_Size / 2)。

- 左图标准2D Torus:传统 TPUv4 架构的典型连接模式(步长 Step=1),数据流必须沿着物理邻居逐跳传递(例如:Node 1 → Node 2 → Node 3)。

- 右图 Twisted 2D Torus:TPUv7 架构演进后的核心模式(引入步长 Step=N),光纤链路不再受限于物理位置,而是实现了“跳跃式互联”,如图中虚线所示,OCS 建立了一条类似“虫洞”的长距离光路,直接将 Node 1 连接至 Node 3(跳过了中间的物理邻居 Node 2)。

图 5 标准 2D Torus 与 Twisted 2D Torus 拓扑对比

理解了Twisted 2D Torus的步长跳跃原理后,我们将视角升维至Twisted 3D Torus。下图展示了 TPUv7 架构中 128 TPU Slice (4x4x8 拓扑) 的实际连接形态,重点描绘了 Cube A与 Cube B之间的扭曲互联,直观揭示了 OCS 如何实现物理位置与逻辑拓扑的彻底解耦。以图中 Z 轴(绿线)为例,位于 Cube A边界的节点 TPU (4,1,4) 并没有像标准3D Torus 4x4x4 拓扑那样回环至自身的起点 TPU (4,1,1),而是通过Twisted 3D Torus和OCS构建类似于“虫洞”的 跳跃式链接 至逻辑相邻的 Cube B 起始节点 TPU (4,1,5)上。

图 6 :TPUv7 128TPU拓扑

3.2 TPUv5e/v6e 与 2D Torus Mesh

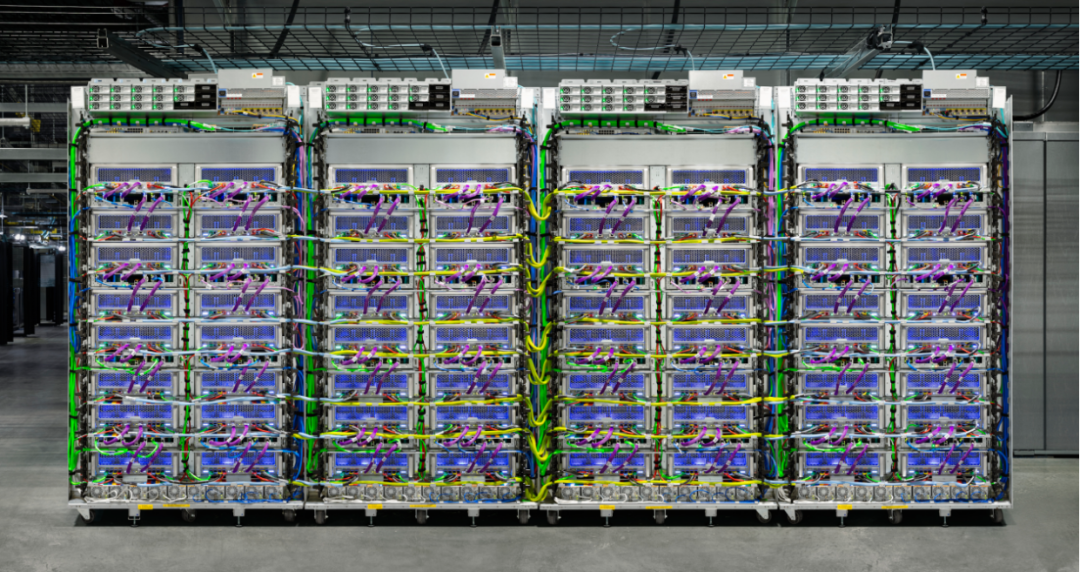

针对延迟敏感的推理任务及中小规模训练场景,Google 推出的 TPUv5e 与 TPUv6e (Trillium) 芯片组采用了追求极致性价比的精简架构设计策略,通过移除高成本的 OCS 光交换层和静态的2D Torus Mesh固定互联架构, 单个Pod最大支持256个TPU, 即由 4 个液冷机柜组成的逻辑 16×16 拓扑网络,而物理层面实现严格X/Y轴的介质分层设计,其中 Y 轴维度的垂直互联完全依赖服务器内部的 PCB 蚀刻背板及连接器实现超低延迟通信,而 X 轴维度的跨机柜横向互联则通过机柜面板上的 QSFP-DD DAC 无源铜缆完成,最终利用长距离线缆将首尾机柜物理连接以闭合环路,从而构建起完整且具备确定性带宽的 2D Torus网络。

图 7 TPUv5e 液冷板与接口布局

4

行业格局深度对比与供应链验证

4.1 Google (ICI) vs AWS (Trainium) vs NVIDIA

维度 | Google TPU (v4/v7) | AWS Trainium (Trn2/3) | NVIDIA (H100/GB200) |

|---|---|---|---|

互联协议 | G-ICI (私有轻量级,Credit-based) | NeuronLink (环) + EFA/SRD (以太网) | NVLink + InfiniBand/RoCE |

网络层级 | 物理隔离:ICI和DCN存储分离 | 相对融合:内部2D Torus,外部走 EFA | 分层架构:Scale-up 与 Scale-out 分层 |

故障恢复 | 物理重构:OCS 旋转镜面隔离坏点 | 协议重传:SRD 协议处理乱序与多路径重传 | 协议重传:依赖IB/RoCE 重传机制 |

软件耦合 | 强耦合:XLA 编译器需感知物理拓扑 | 解耦:软件层网络扁平化,依赖底层硬件重传 | 解耦:CUDA 生态屏蔽底层拓扑差异 |

核心哲学 | 静态极致:通过OCS光交换网络构建确定拓扑 | 动态灵活:依靠以太网多路径解决拥塞 | 带宽堆叠:顶级芯片提供无阻塞带宽 |

表2:Google TPU VS AWS Trainium VS NVIDIA H100/GB200

4.2 行业壁垒:为何难以复制 Google 模式?

Google TPUv7 Pod真正的护城河在于构筑了从物理原子到应用生态的垂直整合闭环:

- 一方面是自研高精度 MEMS 光开关及闭环控制系统涉及精密光学、机械工程与半导体工艺的深度交叉,构筑在物理层面的“原子级”制造门槛是通用网络厂商难以逾越的护城河;

- 另外一方面3D Torus 的效能发挥高度依赖 Orion SDN 控制器 与 XLA 编译器 的深度协同,上层编译器能够拥有底层物理拓扑的“上帝视角”进行精确的算子放置与路由规划,这种垂直整合能力是依赖标准协议栈的厂商所无法复制的;

- 最后,Google作为全世界少数拥有芯片、编译器、框架、模型以及应用的全产业链端到端一条龙服务的公司,利用“训推一体 TPU 芯片 + PyTorch XLA/JAX 原生编译器 + TensorFlow/JAX 框架 + Gemini 模型 + Search/YouTube/Workspace 十亿级应用入口” 构建了不可复制的数据反馈闭环。这种全栈体系所激发的马太效应与正向飞轮,才是 Google 在 AI 军备竞赛中真正的制胜王牌。

4.3 供应链:OCS 生态的全面产业化

根据最新的权威券商研报及供应链深度调研结果显示,Google OCS 的大规模部署已经得到了产业链核心环节的全面交叉验证,构建起了一个从底层芯片到整机集成的稳固生态系统:在底层的物理执行单元层面,以 Silex Microsystems(赛微电子子公司) 为代表的头部 MEMS 代工厂已攻克了 2D MEMS 微镜阵列的高良率量产难题,确保了从 TPUv4 到 TPUv7 世代实现光束精准偏转核心元件的持续供应与技术迭代;与此同时,在整机集成与架构演进方面,以 光迅科技 为代表的厂商已具备 192x192 端口 MEMS-OCS 的交付能力,而 德科立 作为核心集成商 Lumentum 的合作伙伴,正积极推进下一代 320x320 端口超高密度 OCS 的研发与送样,这一高密度趋势与 Google 追求网络架构扁平化的长期愿景高度契合;在精密光学控制环节,以 腾景科技 为代表的厂商通过切入 Tier-1 供应链体系,提供了用于分离 850nm 监控光与 1310nm 业务光的二向色分光镜,补全了实现 OCS 高精度闭环控制系统的关键组件;最后,配合以 中际旭创 为代表的 800G/1.6T 高速光模块厂商,成功打破了 I/O 瓶颈,确立了 TPUv7 集群带宽跨代升级的物理基础。受益于上下游产业链合作共赢生态让Google能够成功落地“硬件即服务 (HaaS)”的金融工程创新:将 OCS 确立为折旧期远长于 GPU(4-5年)的长期基础设施资产,有效解决了算力集群快速迭代与数据中心 15 年租赁周期之间的错配问题,进而从系统层面降低了长期 TCO。

5

架构演进:迈向 CPO 与全光互联的后摩尔时代

随着 TPUv8 及其后续架构的演进,单通道 SerDes 速率突破已 224Gbps 并向 448Gbps 迈进,传统依赖 OSFP 光模块的电气互连已逼近物理极限,CPO(Co-Packaged Optics,共封装光学)将成为突破 I/O 物理边界的必然技术路径。

或许在未来的Google TPU架构中我们预计将见证 Google 3D Torus + OCS 系统迈向“芯片出光、全光直连”的全新范式:光引擎通过异构集成直接封装于 TPU 基板之上,光信号无需经过高损耗的板级电传输,而是从芯片封装直接引出,经由高密度光纤汇聚至机柜后方的盲插背板,无缝对接新一代 320×320 甚至更高维度的OCS 光交换网络。

在后摩尔定律时代,面相AGI的终极算力形态是属于追求极致兼容性的“以太网/InfiniBand 通用生态”,还是属于像 Google 这样将光子技术垂直封装进芯片的“封闭花园”呢?

本文参与 腾讯云自媒体同步曝光计划,分享自微信公众号。

原始发表:2025-12-15,如有侵权请联系 cloudcommunity@tencent.com 删除

评论

登录后参与评论

推荐阅读